## 晶 發 科 技 股 份 有 限 公 司 GI FAR TECHNOLOGY CO., LTD. No. 81, Dongfeng St, Shulin District, 238034, New Taipei City, Taiwan, R.O.C.

AFROR CERTIFICATION

AFROR CERTIFICATION

AFROR CERTIFICATION

AFROR CERTIFICATION

CUSTOMER

:

GFE122032I-GPNE

MODEL NO.

:

GFE122032I-GPNE

VERSION

:

C

DATE

:

2022.11.02

CERTIFICATION : ROHS

| Customer Sign | Approved By | Prepared By | Prepared By |

|---------------|-------------|-------------|-------------|

|               | GIFAR       | GIFAR       | GIFAR       |

|               | 2022.11.02  | 2022,11.02  | 2022.11.02  |

|               | Sidney      | Roger       | Hazel       |

晶 發 科 技 股 份 有 限 公 司 GI FAR TECHNOLOGY CO.,LTD

新北市樹林區東豐街81號

No. 81, Dongfeng St, Shulin District, 238034, New Taipei City, Taiwan, R.O.C. TEL: +886-2-8684-1188 FAX: +886-2-8684-8532

PAGE 1/19 P-18-09C

### 晶發科技股份有限公司 GI FAR TECHNOLOGY CO., LTD. No. 81, Dongfeng St, Shulin District, 238034, New Taipei City, Taiwan, R.O.C.

### **Revision Record**

| Data(y/m/d) | Ver. | Description            | page |

|-------------|------|------------------------|------|

| 2012.07.05  | A    | Specification released |      |

| 2017.03.24  | В    | 修改公司抬頭、格式統一            |      |

| 2022.11.02  | С    | 更新公司抬頭認證圖示             |      |

|             |      |                        |      |

|             |      |                        |      |

|             |      |                        |      |

|             |      |                        |      |

|             |      |                        |      |

|             |      |                        |      |

|             |      |                        |      |

|             |      |                        |      |

|             |      |                        |      |

|             |      |                        |      |

|             |      |                        |      |

|             |      |                        |      |

|             |      |                        |      |

PAGE 2/19 P-18-09C

# 晶 發 科 技 股 份 有 限 公 司 GI FAR TECHNOLOGY CO., LTD. No. 81, Dongfeng St, Shulin District, 238034, New Taipei City, Taiwan, R.O.C.

### **CONTENTS**

| 1. | Scop  | oe\                                              | <br>4  |

|----|-------|--------------------------------------------------|--------|

| 2. | Prod  | uct Specifications                               | <br>4  |

|    | 2.1   | General                                          | <br>4  |

|    | 2.2   | Mechanical Characteristics                       | <br>4  |

|    | 2.3   | Absolute Maximum Ratings                         | <br>5  |

|    | 2.4   | Electrical Characteristics                       | <br>5  |

|    | 2.5   | Optical Characteristics Absolute maximum ratings | <br>5  |

|    | 2.6   | Optical Characteristics                          | <br>6  |

| 3. | Relia | ability                                          | <br>7  |

| 4. | Ope   | rating Instructions                              | <br>8  |

|    | 4.1   | Input signal Function                            | <br>8  |

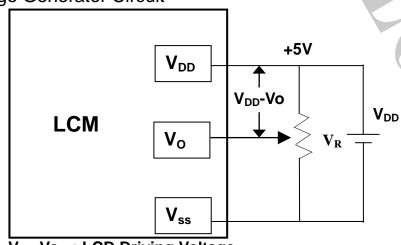

|    | 4.2   | Voltage Generator Circuit                        | <br>8  |

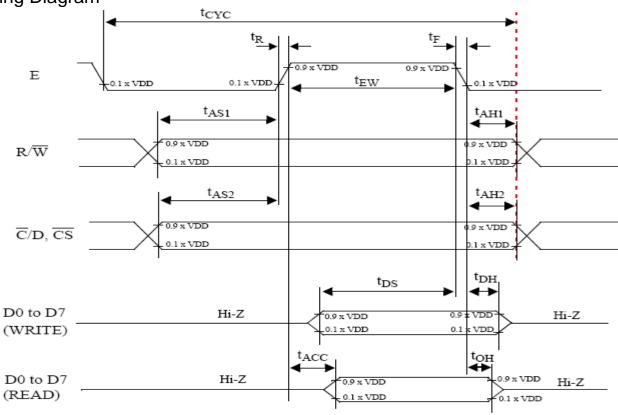

|    | 4.3   | Timing Diagram                                   | <br>9  |

|    | 4.4.  | Display Control Instructions and Registers       | <br>10 |

| 5  | Note  | s                                                | <br>17 |

| 6  | Ope   | ration Precautions                               | 17     |

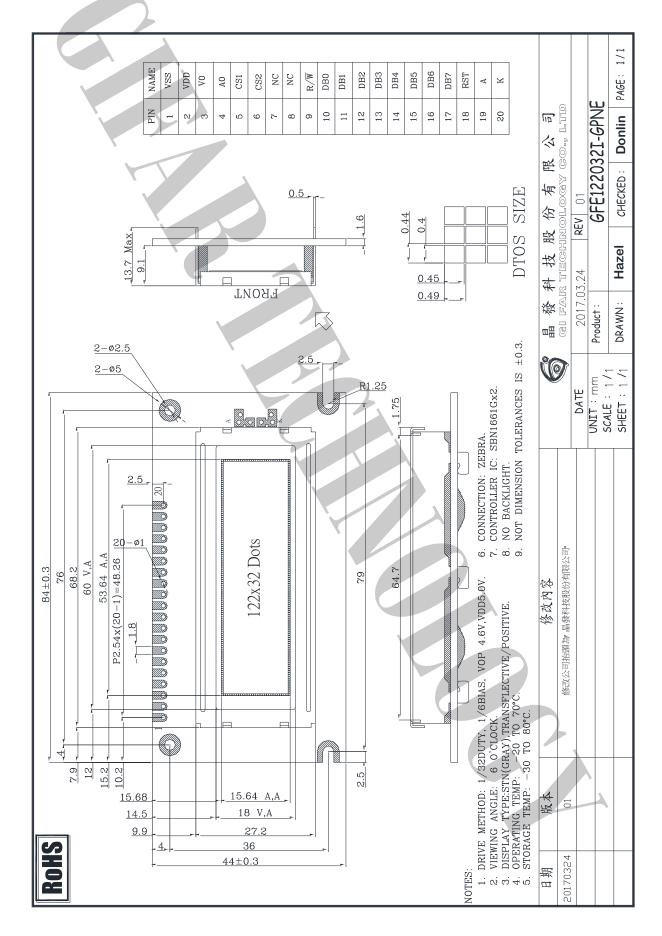

| 7  | LCM   | Dimensions                                       | 18     |

| 8  | Pack  | age information                                  | 20     |

|    | Арре  | endix : Inspection Standard                      |        |

PAGE 3/19 P-18-09C

### 1. SCOPE

This specification covers the engineering requirements for the GFE122032I-GPNE liquid crystal module.

### 2. PRODUCT SPECIFICATIONS

### 2.1 General

- 122 × 32 dot matrix LCD

- STN (GRAY), Positive mode LCD panel

- Transflective Wide temperature type

- 6 o'clock

- Multiplexing driving: 1/32duty, 1/6bias

- Controller IC : SBN1661G or Compatible

- Backlight: NO Backlight

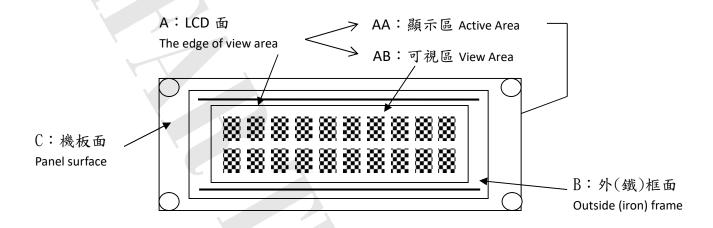

### 2.2 Mechanical Characteristics

| Item             | Value                   | Unit |

|------------------|-------------------------|------|

| Number of dots   | 122X32                  | Dot  |

| Dot size         | 0.4 X0.45               | mm   |

| Dot pitch        | 0.44 X0.49              | mm   |

| Module dimension | 84(W) X 44(H) X 13.7(T) | mm   |

| Viewing Area     | 60 (W) X 18 (H)         | mm   |

| Active Area      | 53.64 (W) X 15.64 (H)   | mm   |

| Module           | NO Connector            |      |

PAGE 4/19 P-18-09C

## 晶 發 科 技 股 份 有 限 公 司 GI FAR TECHNOLOGY CO., LTD No. 81, Dongfeng St, Shulin District, 238034, New Taipei City, Taiwan, R.O.C.

### 2.3 Absolute Maximum Ratings (Without LED back-light)

| Characteristic            | Symbol          | Unit | Value                        |

|---------------------------|-----------------|------|------------------------------|

| Operating Voltage (logic) | $V_{DD}$        | V    | -0.3 to +7.0                 |

| Input Voltage             | V <sub>IN</sub> | V    | -0.3 to V <sub>DD</sub> +0.3 |

Note 1: Referenced to V<sub>SS</sub>=0V

### 2.4 Electrical Characteristics (Without LED back-light)

| Characteristic           | Symbol                           | Condition               | Min.               | Тур. | Max.        | Unit |

|--------------------------|----------------------------------|-------------------------|--------------------|------|-------------|------|

| Operating Voltage(logic) | V <sub>DD</sub> -V <sub>SS</sub> | -                       | 4.7                | 5.0  | 5.3         | V    |

| Input Voltage            | V <sub>IH</sub>                  |                         | 0.8V <sub>DD</sub> |      | $V_{DD}$    | V    |

| Input Voltage            | V <sub>IL</sub>                  | -                       | V <sub>SS</sub>    |      | $0.2V_{DD}$ | V    |

| Output Voltage           | V <sub>OH</sub>                  | I <sub>OH</sub> =-0.1mA | 0.8V <sub>DD</sub> |      | $V_{DD}$    | V    |

### 2.5 Optical Characteristics Absolute maximum ratings

| Item                        | Symbol | Rating | Unit |

|-----------------------------|--------|--------|------|

| Operating temperature range | Тор    | -20~70 | °C   |

| Storage temperature range   | Tst    | -30~80 | °C   |

PAGE 5/19 P-18-09C

# 晶 發 科 技 股 份 有 限 公 司 GI FAR TECHNOLOGY CO., LTD No. 81, Dongfeng St, Shulin District, 238034, New Taipei City, Taiwan, R.O.C.

### 2.6. Optical Characteristics

1/32 duty, 1/6 bias, Vop=4.6 V, Ta=25°C

|                     | 1/32 daty, 1/6 blas, vop=4:6 v, 1a=2 |                 |      |      |       | 1.0 v, 1a-20 c |

|---------------------|--------------------------------------|-----------------|------|------|-------|----------------|

| Item                | Symbol                               | Conditions      | Min. | Тур. | Max   | Reference      |

| Driving voltage     | Vop                                  |                 | i    | 4.6  |       |                |

| Viewing angle       | θ1 · θ2                              | C≥2.0,∅=0°<br>C | 30°  | -    | -     | Notes 1 & 2    |

| Contrast            | C                                    | θ=5°, Ø=0°      | 2.0  | -    | -     | Note 3         |

| Response time(rise) | ton                                  | θ=5°, Ø=0°      | -    | -    | 260ms | Note 4         |

| Response time(fall) | toff                                 | θ=5°, Ø=0°      | -    | -    | 380ms | Note 4         |

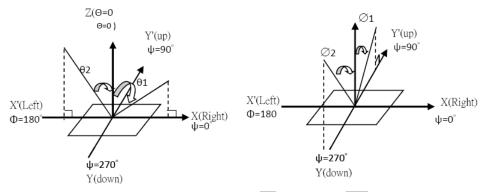

Note 1: Definition of angles  $\theta$  and  $\emptyset$

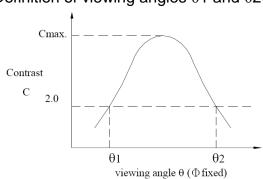

Note 2: Definition of viewing angles  $\theta$ 1 and  $\theta$ 2

Note: Optimum viewing angle with the naked eye and viewing angle θ at Cmax. Above are not always the same

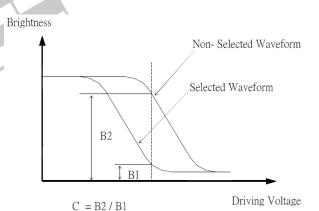

Note 3: Definition of contrast C

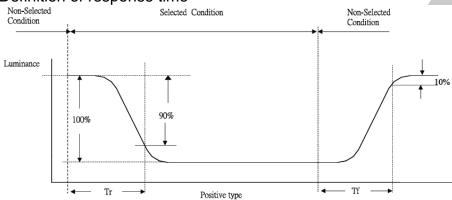

Note 4: Definition of response time

PAGE 6/19 P-18-09C

# 晶 發 科 技 股 份 有 限 公 司 GI FAR TECHNOLOGY CO., LTD. No. 81, Dongfeng St, Shulin District, 238034, New Taipei City, Taiwan, R.O.C.

### 3. RELIABILITY

| NO. | ITEM                               | COND           | DITION                 | STANDARD                     | NOTE      |

|-----|------------------------------------|----------------|------------------------|------------------------------|-----------|

| 1   | High Temp. Storage                 | 80°C           | 120 hrs                | Appearance<br>Without defect |           |

| 2   | Low Temp. Storage                  | -30°C          | 120 hrs                | Appearance<br>Without defect |           |

| 3   | High Temp. & High<br>Humi. Storage | 40°C<br>90% RH | 120 hrs                | Appearance<br>Without defect |           |

| 4   | High Temp.<br>Operating Display    | 70°C           | 120 hrs                | Appearance<br>Without defect |           |

| 5   | Low Temp.<br>Operating Display     | <b>-20</b> °C  | 120 hrs                | Appearance<br>Without defect |           |

| 6   | Thermal Shock                      |                | → 70°C,30min.<br>vcle) | Appearance<br>Without defect | 10 cycles |

<sup>\*\*</sup> Dissipation current, contrast and display functions

PAGE 7/19 P-18-09C

<sup>\*\*</sup> Polarizing filter deterioration, other appearance defects

<sup>\*\*</sup> The function test shall be conducted after 4hours storage at the normal temperature and humidity after remove from the test chamber.

### 晶發科技股份有限公司 GI FAR TECHNOLOGY CO., LTD. No. 81, Dongfeng St, Shulin District, 238034, New Taipei City, Taiwan, R.O.C.

### 4. OPERATING INSTRUCTIONS

### 4.1 Input signal Function

| Pin No | Symbol | Function                                                                                                              |

|--------|--------|-----------------------------------------------------------------------------------------------------------------------|

| 1      | Vss    | Signal ground (GND)                                                                                                   |

| 2      | Vdd    | Power supply for logic (+5V)                                                                                          |

| 3      | Vo     | Operating voltage for LCD (variable)                                                                                  |

| 4      | A0     | Start enable signal to read or write the data                                                                         |

| 5      | CS1    | Chip1 enable (segment 1 to segment 64),Active high                                                                    |

| 6      | CS2    | Chip2 enable (segment 65 to segment 128),Active high                                                                  |

| 7      | NC     | NC                                                                                                                    |

| 8      | NC     | NC                                                                                                                    |

| 9      | R/W    | Data read & write                                                                                                     |

| 10-13  | DB0~DB | Four low order bi-directional three-state data bus lines. Used                                                        |

| 10-13  | 3      | for data transfer between the MPU and the LCD module.                                                                 |

| 14-17  | DB4~DB | Four high order bi-directional three-state data bus lines. Used for data transfer between the MPU and the LCD module. |

| 14-17  | 7      | DB7 can be used as a busy flag.                                                                                       |

| 18     | RST    | Reset signal                                                                                                          |

| 19     | NC     | NC                                                                                                                    |

| 20     | NC     | NC                                                                                                                    |

### 4.2 Voltage Generator Circuit

V<sub>DD</sub>-Vo : LCD Driving Voltage

$V_R$ : 10K~20K

> PAGE 8/19 P-18-09C

# 晶 發 科 技 股 份 有 限 公 司 GI FAR TECHNOLOGY CO., LTD. No. 81, Dongfeng St, Shulin District, 238034, New Taipei City, Taiwan, R.O.C.

4.3 Timing Diagram

| symbol                          | parameter                                   | min. | max. | test conditions                        | unit |

|---------------------------------|---------------------------------------------|------|------|----------------------------------------|------|

| t <sub>AS1</sub>                | Address set-up time with respect to R/W     | 20   |      |                                        | ns   |

| t <sub>AS2</sub>                | Address set-up time with respect to C/D, CS | 20   |      |                                        | ns   |

| t <sub>AH1</sub>                | Address hold time with respect to R/W       | 10   |      |                                        | ns   |

| t <sub>AH2</sub>                | Address hold time respect with to C/D, CS   | 10   |      |                                        | ns   |

| t <sub>F</sub> , t <sub>R</sub> | Enable (E) pulse falling/rising time        |      | 15   |                                        | ns   |

| tcyc                            | System cycle time                           | 1000 |      | Note 1                                 | ns   |

| t <sub>EWR</sub>                | Enable pulse width for READ                 | 100  |      |                                        | ns   |

| t <sub>EWW</sub>                | Enable pulse width for WRITE                | 80   |      |                                        | ns   |

| t <sub>DS</sub>                 | Data setup time                             | 80   |      | -3                                     | ns   |

| t <sub>DH</sub>                 | Data hold time                              | 10   |      |                                        | ns   |

| tacc                            | Data access time                            |      | 90   | CL= 100 pF.                            | ns   |

| tон                             | Data output hold time                       | 10   | 60   | Refer to Fig. 23.                      | ns   |

| 1,771,71                        |                                             |      |      | 10.00 0.000 U.V. 10.00 U.V. 10.00 U.V. |      |

PAGE 9/19 P-18-09C

### 4.4.DISPLAY CONTROL INSTRUCTIONS AND REGISTERS

### 4.4.1 Registers and their states after hardware RESET

The SBN1661G\_X has a set of registers. To ensure proper operation of the devices, these registers must be programmed with proper values after hardware reset.

The registers and their states after RESET is given in Table 1.

### Table 1 Registers and their states after RESET

| Register Name                      | Description                                                                                                                                           | States after<br>RESET |

|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Display ON/OFF Register            | The Display ON/OFF Register is a 1-bit register. After RESET, its value is LOW and, therefore, the LCD display is turned OFF.                         | 0                     |

| Display Start Line Register        | The Display Start Line Register is a 6-bit register. After RESET, its value is 0 0000 and Row0 of the Display Data Memory is mapped to COM0.          | 00 0000               |

| Page Addres Register               | The Page Address Register is a 3-bit register. After RESET, its value is 11 and, therefore, it points to Page 7 of the Display Data Memory.           | 111                   |

| Column Address Register            | The Column Address Register is a 7-bit register. After RESET, its value is 000 0000 and, therefore, it points to column 0 of the Display Data Memory. | 000 0000              |

| Static Drive ON/OFF Register       | The Static Drive ON/OFF Register is a 1-bit register. After RESET, its value is LOW and static display is turned OFF.                                 | 0                     |

| Duty Select Register               | The Duty Select Register is a 1-bit register. After RESET, its value is HIGH and 1/32 display duty is selected.                                       | 1                     |

| Column/Segment Mapping<br>Register | The Column/Segment Mapping Register is a 1-bit register. After RESET, its value is LOW and normal mapping is selected.                                | 0                     |

| Status Register                    | The Status Register shows the current state of the SBN1661G_X. It is a 4-bit register, with each bit showing the status of a programmed function.     | 0000 0000             |

#### 4.4.2 Display ON/OFF and the Display ON/OFF Register

The Display ON/OFF Register is a 1-bit Register. When this bit is progammed to HIGH, the display is turned ON. When this bit is programmed to LOW, the display is turned OFF and all COMMON and SEGMENT outputs are set to VDD.

To program this register, the setting of control bus is given in Table 2 and the setting of the data bus is given in Table 3.

Table 2 Setting of the control bus for programming the Display ON/OFF Register

| C/D | E/(RD) | R/W(WR) |

|-----|--------|---------|

| 0   | 1      | 0       |

#### Table 3 Setting of the data bus for programming the Display ON/OFF Register

| D7(MSB) | D6 | D5 | D4 | D3 | D2 | D1 | D0(LSB) |

|---------|----|----|----|----|----|----|---------|

| 1       | 0  | 1  | 0  | 1  | 1  | 1  | D0      |

When D0=1, the code is AF(Hex) and the display is turned ON. When D0=0, the code is AE(Hex) and the display is turned OFF.

> P-18-09C PAGE 10/19

No. 81, Dongfeng St, Shulin District, 238034, New Taipei City, Taiwan, R.O.C.

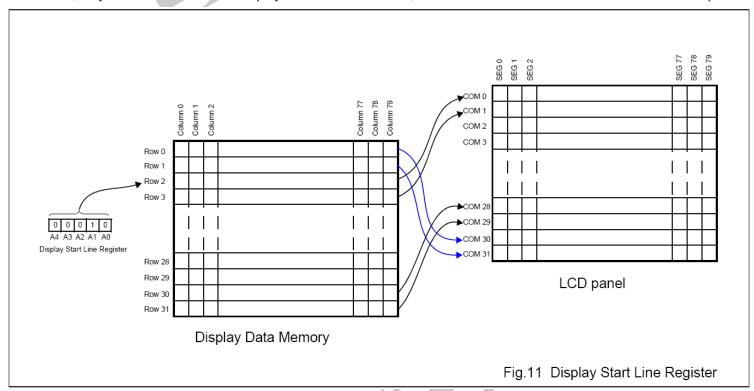

### 4.4.3 Display Start Line and the Display Start Line Register

The Display Start Line Register is a 5-bit Register. It points at the first row of a block of the Display Data Memory, which will be mapped to COM0. The length of the block of the memory can be 32 rows or 16 rows, which is decided by the Duty Select Register. For example, if the Display Start Line Register is programmed with 00010 (decimal 2) and display duty is 1/32, then Row2 of the Display Data Memory will be mapped to COM0 of LCD panel, Row3 to COM1, Row4 to COM2, Row30 to COM28, Row31 to COM29, Row0 to COM30, and finally Row1 to COM31, as illustrated in Fig. 11. However, in this case, only Row2~Row17 can be displayed on COM0~COM15, as COM16~COM31 are not available from the chip.

To program this register, the setting of the control bus is given in Table 4 and the setting of the data bus is given in Table 5.

Table 4 The setting of the control bus for programming the Display Start Line Register

| C/D | E/(RD) | R/W(WR) |

|-----|--------|---------|

| 0   | 1      | 0       |

Table 5 The setting of the data bus for programming the Display Start Line Register

| D7(MSB) | D6 | D5 | D4 | D3 | D2 | D1 | D0(LSB) |

|---------|----|----|----|----|----|----|---------|

| 1       | 1  | 0  | A4 | A3 | A2 | A1 | A0      |

A4, A3, A2, A1, and A0 are Start Line address bits and they can be programmed with a value in the range from 0 to 31. Therefore, the code can be from 1100 0000 (C0 Hex) to 1101 1111 (DF Hex).

PAGE 11/19 P-18-09C

No. 81, Dongfeng St, Shulin District, 238034, New Taipei City, Taiwan, R.O.C.

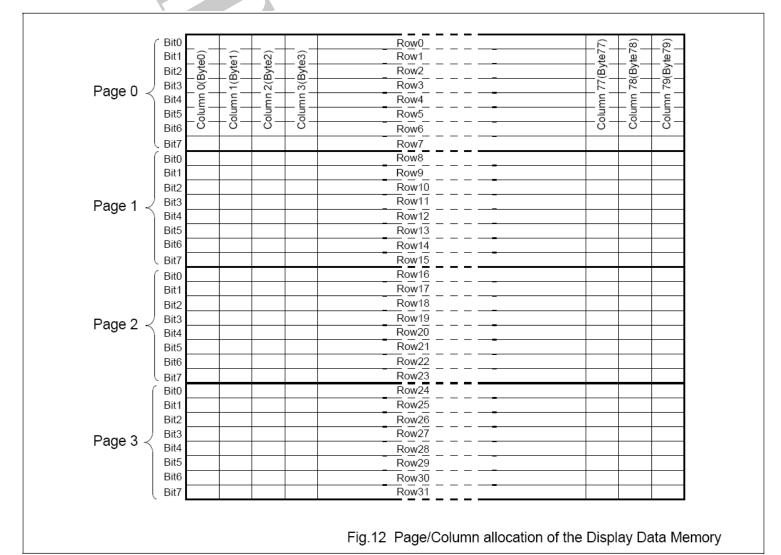

### 4.4.4 Display Data Memory Page and the Page Address Register

The on-chip Display Data Memory is divided into 4 pages: Page 0, Page 1, Page 2, and Page 3, with each page having 80 bytes in horizontal direction. Page 0 is from Row 0 to Row 7, Page 1 from Row 8 to Row 15, Page 2 from Row 16 to Row 23, and Page 3 from Row 24 to Row 31, as shown in Fig 12. When the host microtroller intends to perform a READ/WRITE operation to the Display Data Memory, it has to program the Page Adrress Register to indicate which page it intends to access.

To program this register, the setting of the control bus is given in Table 6 and the setting of the data bus is given in Table 7.

Table 6 The setting of the control bus for programming the Page Address Register

| C/D | E/(RD) | R/W(WR) |

|-----|--------|---------|

| 0   | 1      | 0       |

Table 7 The setting of the data bus for programming the Page Address Register

| D7(MSB) | D6 | D5 | D4 | D3 | D2 | D1 | D0(LSB) |

|---------|----|----|----|----|----|----|---------|

| 1       | 0  | 1  | 1  | 1  | 0  | A1 | A0      |

A1and A0 are page address bits and can be programmed with a value in the range from 0 to 3. A1A0=00 selects Page 0, A1A0=01 selects Page 1, A1A0=10 selects Page 2, and A1A0=11 selects Page 3. Therefore, the code can be from 1011 1000 (B8 Hex) to 1011 1011 (BB Hex).

PAGE 12/19 P-18-09C

No. 81, Dongfeng St, Shulin District, 238034, New Taipei City, Taiwan, R.O.C.

### 4.4.5 Column address and the Column Address Register

The Column Address Register points at a column of the Display Data Memory which the host microcontroller intends to perform a READ/WRITE operation. The Column Address Register automatically increments by 1 after a READ or WRITE operation is finished. When the Column Address Register reaches 79, it overflows to 0. Please refer to Fig.12 for the column sequence in a page of the Display Data Memory.

To program this register, the setting of the control bus is given in Table 8 and the setting of the data bus is given in Table 9.

Table 8 The setting of the control bus for programming the Column Address Register

| C/D | E/(RD) | R/W(WR) |

|-----|--------|---------|

| 0   | 1      | 0       |

Table 9 The setting of the data bus for programming the Column Address Register

| D7(MSB) | D6 | D5 | D4 | D3 | D2 | D1 | D0(LSB) |

|---------|----|----|----|----|----|----|---------|

| 0       | A6 | A5 | A4 | A3 | A2 | A1 | A0      |

A6~A0 are column address bits and can be programmed with a value in the range from 0 to 79. Therefore, the code can be from 0000 0000 (00 Hex) to 0100 1111 (4F Hex).

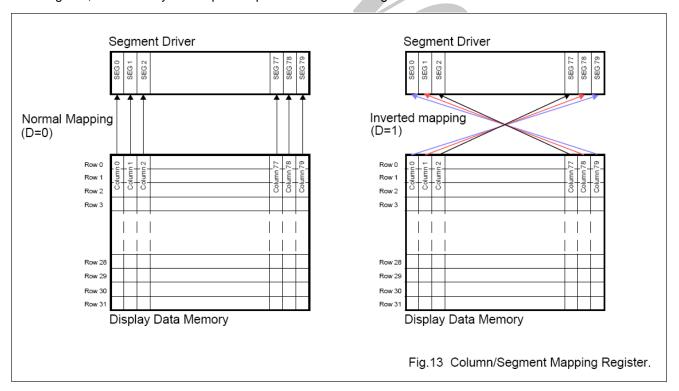

### 4.4.6 Mapping between Memory Cloumns and Segments and the Column/Segment Mapping Register

The Column/Segment Mapping Register is a 1-bit register and selects the mapping relation between the column outputs of the Display Data Memory and the Segment outputs SEG0~SEG79.

If this register is programmed with HIGH, then the data from column 79 of the Display Data Memory will be output from SEG0. This type of mapping is called *inverted mapping*.

If this register is programmed with LOW, then data from column 0 of the Display Data Memory will be output from SEG0. This type of mapping is called *normal mapping*.

By use of this register, the flexibility of component placement and routing on a PCB can be increased.

PAGE 13/19 P-18-09C

No. 81, Dongfeng St, Shulin District, 238034, New Taipei City, Taiwan, R.O.C.

To program this register, the setting of the control bus is given in Table 10 and the setting of the data bus is given in Table 11.

Table 10 The setting of the control bus for programming the Column/Segment Mapping Register

| C/D | E/(RD) | R/W(WR) |

|-----|--------|---------|

| 0   | 1      | 0       |

Table 11 The setting of the data bus for programming the Memory/Segment Mapping Register

| D7(MSB) | D6 D5 | D4 | D3 | D2 | D1 | D0(LSB) |

|---------|-------|----|----|----|----|---------|

| 1       | 0 1   | 0  | 0  | 0  | 0  | D       |

The least significant bit D can be programmed with either 0 or 1. Therefore, the codes are A0 Hex or A1 Hex.

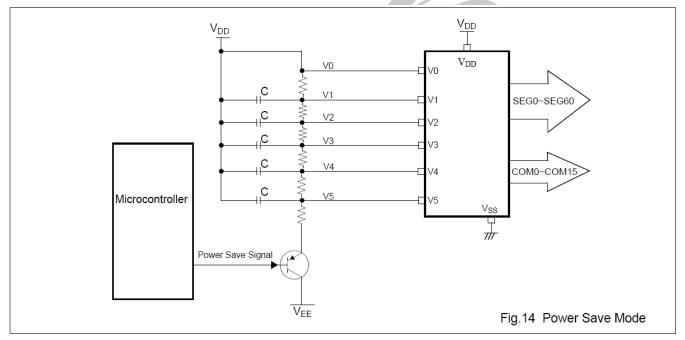

### 4.4.7 Static Drive ON/OFF and the Static Drive ON/OFF register

The Static Drive ON/OFF Register is a 1-bit register. It is used to turn ON or OFF the Static Drive Mode of the SBN1661G\_X. When this register is programmed with HIGH, Static Drive Mode is turned ON and the device enters into Static Drive Mode, in which the internal clock circuitry is disabled and the switching of the internal logic is suspended. When this register is programmed with LOW, Static Drive Mode is turned OFF and the chip returns to normal operation.

This register is used in combination with the Display ON/OFF register to make the current consumption of the LCD

module reduced to almost static level. By turning OFF the display and turning ON the static drive mode, the chip is configured into the following state:

all COMMON and SEGMENT outputs are set to VDD,

on-chip oscillator or external clock is inhibited and internal logic circuit stays idle,

OSC2 is in floating state (please refer to Section 11, On-chip RC Oscillator), and

the state of registers and the data of the Display Data Memory are kept unchanged.

In addition to turning ON the static drive mode and turning OFF the display, to really reduce the power consumption of the LCD module, the host microcontroller should also send out a power-save signal to turn off the PNP transistor in the bias circuit, such that the current flow from VDD to VEE can be cut off, as shown in Fig. 14.

PAGE 14/19 P-18-09C

No. 81, Dongfeng St, Shulin District, 238034, New Taipei City, Taiwan, R.O.C.

To program this register, the setting of the control bus is given in Table 12 and the setting of the data bus is given in Table 13.

Table 12 The setting of the control bus for programming the Static Drive ON/OFF Regist

| C/D | E/(RD) | R/W(WR) |

|-----|--------|---------|

| 0   | 1      | 0       |

Table 13 The setting of the data bus for programming the Static Drive ON/OFF Register

| D7(MSB) | D6 | D5 | D4 | D3 | D2 | D1 | D0(LSB) |

|---------|----|----|----|----|----|----|---------|

| 1       | 0  | 1  | 0  | 0  | 1  | 0  | D       |

The least significant bit D0 can be programmed with either 0 or 1. Therefore, the code is A4 Hex or A5 Hex.

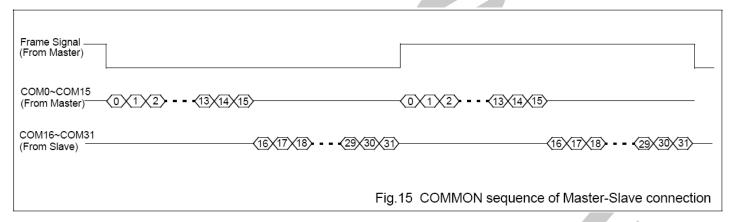

### 4.4.8 Select Duty and the Select Duty Register

The Select Duty Register is a 1-bit register. If it is programmed with HIGH, 1/32 display duty is selected. If it is programmed with LOW, 1/16 display duty is selected.

To program this register, the setting of the control bus is given in Table 14 and the setting of the data bus is given in Table 15.

Table 14 The setting of the control bus for programming the Select Duty Register

| C/D | E/(RD) | R/W(WR) |

|-----|--------|---------|

| 0   | 1      | 0       |

Table 15 The setting of the data bus for programming the Select Duty Register

| D7(MSB) | D6 | D5 | D4 | D3 | D2 | D1 | D0(LSB) |

|---------|----|----|----|----|----|----|---------|

| 1       | 0  | 1  | 0  | 1  | 0  | 0  | D       |

The least significant bit D can be programmed with either 0 or 1. Therefore, the code is A8 Hex or A9 Hex.

In a Master-Slave connection using the SBN1661G\_M18 or the SBN1661G\_M02 as the master, COM0~COM15 will be from the master and COM16~COM31 will be from the slave. The Select Duty Register of both the Master and the Slave should be programmed with HIGH to select 1/32 duty. Fig.15 shows the COMMON sequence of this connection.

This register is not available in the SBN0080G\_S18 and the SBN0080G\_S02, because both the devices are purely Segment Drivers and their duty cycle is decided by the FR and the CL from the master.

PAGE 15/19 P-18-09C

No. 81, Dongfeng St, Shulin District, 238034, New Taipei City, Taiwan, R.O.C.

### 4.4.9 Status Read and Status Register

The Status Register shows the current state of the SBN1661G\_X. It can be read by the host microcontroller. Bit 7~4 shows the status and Bit 3~0 are always fixed at 0.

To read the Status Register, the setting of the control bus is given in Table 16, the bit allocation is given in Table 17 and the description for each bit is given in Table 18.

#### Table 16 The setting of the control bus for reading the Status Register

| C/D | E/(RD) | R/W(WR) |

|-----|--------|---------|

| 0   | 0      | 1       |

#### Table 17 The Status Register bit allocation

| D7(MSB) | D6      | D5     | D4    | D3 | D2 | D1 | D0(LSB) |

|---------|---------|--------|-------|----|----|----|---------|

| BUSY    | MAPPING | ON/OFF | RESET | 0  | 0  | 0  | 0       |

#### Table 18 The Status Register bit description.

| Bit                                                                         | Description                                                                              |  |  |  |  |

|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------|--|--|--|--|

| BUSY                                                                        | BUSY=1 indicates that the SBN1661G_X is currently busy and can not accept new command or |  |  |  |  |

|                                                                             | data. The SBN1661G_X is executing a command or is in the process of reset.               |  |  |  |  |

| BUSY=0 indicates that the SBN1661G_X is not busy and is ready to accept new |                                                                                          |  |  |  |  |

|                                                                             | data.                                                                                    |  |  |  |  |

| MAPPING                                                                     | MAPPING=1 indicates that the Column/Segment Mapping Register has been programmed with    |  |  |  |  |

|                                                                             | a value of "1" and the SEG0 is mapped to Column 79 of the Display Data Memory (inverted  |  |  |  |  |

|                                                                             | mapping).                                                                                |  |  |  |  |

| MAPPING=0 indicates that the Column/Segment Mapping Register has been prog  |                                                                                          |  |  |  |  |

|                                                                             | a value of "0" and the SEG0 is mapped to Column 0 of the Display Data Memory (normal     |  |  |  |  |

|                                                                             | mapping).                                                                                |  |  |  |  |

| ON/OFF                                                                      | The ON/OFF bit indicates the current of status of display.                               |  |  |  |  |

|                                                                             | If ON/OFF=0, then the display has been turned ON.                                        |  |  |  |  |

|                                                                             | If ON/OFF=1, then the display has been turned OFF.                                       |  |  |  |  |

|                                                                             | Note that the polarity of this bit is inverse to that of the Display ON/OFF Register.    |  |  |  |  |

| RESET                                                                       | RESET=1 indicates that the SBN1661G_X is currently in the process of being reset.        |  |  |  |  |

|                                                                             | RESET=0 indicates that the SBN1661G_X is currently in normal operation.                  |  |  |  |  |

PAGE 16/19 P-18-09C

### 5. NOTES

### Safety

• If the LCD panel breaks, be careful not to get the liquid crystal in your mouth. If the liquid crystal touches your skin or clothes, wash it off immediately using soap and plenty of water.

### **Handling**

- Avoid static electricity as this can damage the CMOS LSI.

- The LCD panel is plate glass; do not hit or crush it.

- Do not remove the panel or frame from the module.

- The polarizing plate of the display is very fragile; handle it very carefully

### Mounting and Design

- Mount the module by using the specified mounting part and holes.

- To protect the module from external pressure, leave a small gap by placing transparent plates

(e.g. acrylic or glass) on the display surface, frame, and polarizing plate

- Design the system so that no input signal is given unless the power-supply voltage is applied.

- Keep the module dry. Avoid condensation, otherwise the transparent electrodes may break.

### <u>Storage</u>

- Store the module in a dark place where the temperature is 25 °C±10 °C and the humidity below 65% RH.

- Do not store the module near organic solvents or corrosive gases.

- Do not crush, shake, or jolt the module (including accessories).

### Cleaning

- Do not wipe the polarizing plate with a dry cloth, as it may scratch the surface.

- Wipe the module gently with soft cloth soaked with a petroleum benzine.

- Do not use ketonic solvents (ketone and acetoe) or aromatic solvents (toluene and xylene), as they may damage the polarizing plate.

### 6. OPERATION PRECAUTIONS

Any changes that need to be made in this specification or any problems arising from it will be dealt with quickly by discussion between both companies.

Quality warranty period: Within one year after shipment date (excluding abnormal usage way and abnormal environments.)

PAGE 17/19 P-18-09C

No. 81, Dongfeng St, Shulin District, 238034, New Taipei City, Taiwan, R.O.C.

### 7. LCM Dimension

# 晶 發 科 技 股 份 有 限 公 司 GI FAR TECHNOLOGY CO., LTD, No. 81, Dongfeng St, Shulin District, 238034, New Taipei City, Taiwan, R.O.C.

Tio. or, bonglong of, original blother, 20000 i, non-taiper only, failuring

### 8. PACKAGE INFORMATION

| 1 | 1 Tray :              | 14 pcs (modules)                             |

|---|-----------------------|----------------------------------------------|

| 2 | 1 stack :             | 6 tray +1 Cover tray                         |

| 3 | 1 Carton :            | (1 Cover tray + 6 tray )x 3 stack            |

| 4 | Total pcs :           | 1 Carton (14 pcs*6 tray * 3 stack) = 252 pcs |

| 5 | Carton size = NO. 17: | 495*315*435mm                                |

| 7 | Net weight :          | 7.9 KG                                       |

| 8 | Gross weight :        | TBD KG                                       |

- \*\* 包裝示意圖片

- 一個 tray 盤 可放 14PCS 模組

6盤+1空盤=1疊,一箱可放入3疊

● 使用 17 號箱,可放入 3 疊,並使用防震材將旁邊空隙填滿

PAGE 19/19 P-18-09C

### 出貨檢驗標準書 Shipping inspection standard

| 核准          | 審核         | 作成      |  |  |

|-------------|------------|---------|--|--|

| Approved by | Checked by | Made by |  |  |

| ANDY        | JACKY      | RUBY    |  |  |

#### 1.目的 Purpose:

規範出貨產品之檢驗項目及判斷標準,確保產品出貨能滿足客戶要求。

Standardize the inspection items and judgment standards to ensure the products that shipped out can meet customer's requirements.

#### 2. 範圍 Area:

適用於出廠之所有產品。

Applicable to all products shipped from the factory.

- 3.名詞解釋 Explanation of terms:

- 3-1 主要缺陷:亦會造成功能缺失或嚴重外觀缺陷。

Major Defects: It also causes loss of function or serious appearance defects.

- 3-2 次要缺陷:稍有缺陷但不影響客戶使用。

Minor defect: Slightly defective but does not affect customer use.

- 4.檢驗體制 Inspection system:

- 4-1 抽樣計劃:依 ANSI/ASQ Z1.4 一般檢驗水準Ⅱ 之 正常檢驗一次抽驗方案。

Sampling plan: According to ANSI/ASQ Z1.4 general inspection level Ⅱ the normal inspection one-time sampling plan.

- 4-2 允收水準 Acceptable Level:(AQL)

主要缺陷 Major defect:0.4% 次要缺陷 Minor defect:0.65%

- 5.檢驗條件 Inspection conditions:

- 5-1 使用相關之檢測儀器及測試、量測工具。

Use relevant testing instrument, testing and measuring tools.

- 5-2 環境要求:其條件需控制在常溫下 23℃±3℃及溼度 70%RH 以下。

Environmental requirements: The conditions should be controlled at room temperature 23℃±3℃ and humidity below 70%RH.

- 5-3 外觀檢驗:須在 380±20% LUX 的白色日光燈下,其目視距離需於產品離 30±5 cm 檢驗。 Appearance inspection: Under the white fluorescent lamp of 380±20% LUX, the visual distance shall be checked above the product 30±5 cm.

- 5-4 電性測試 Electrical Testing:

- 5-4-1 有背光之產品需關燈並在 5~300Lux±3%下檢驗。

The products with backlight should be tested at 5~300±3% Lux.

- 5-4-2 無背光之產品需開燈並在 60~300Lux±3%白色日光燈下檢驗。

Products without backlight need to be turned on and tested under 60~300 ± 3% LUX white fluorescent lamps.

- 5-5 檢查視角依產品視角方向。

Check the viewing angle according to the product viewing angle.

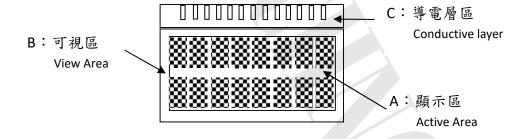

5-6 其不良現象檢視區域 Bad phenomenon View area 5-6-1 適用種類 Applicable category: COB、TFT

5-6-2 適用種類 Applicable category: COG、TAB、TN

### 6. 檢驗標準 Inspection standards

СОВ

| 種類 C | Category                  |                                                                                                                              |                                                                                                                                                                                                                                   | СС                                                                 | В                                                               |                  |                         |                         |

|------|---------------------------|------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------------------------------------|------------------|-------------------------|-------------------------|

| 編號   | 檢驗項目                      | 檢驗F                                                                                                                          | 檢驗內容及判定標準                                                                                                                                                                                                                         |                                                                    |                                                                 |                  | 類別                      | 缺陷等級                    |

| No.  | Item                      | Inspection                                                                                                                   | n Content &                                                                                                                                                                                                                       | Standard                                                           |                                                                 | Zone             | Category                | Level                   |

|      |                           | 黑點、刺傷…等圓狀<br>Black dot、Stab…and other<br>round shape                                                                         | 兩點距離須超過 $5\mathrm{mm}$ Two points have to be $\geq 5\mathrm{mm}$ $\varphi\mathrm{(mm)}\qquad\qquad \qquad \qquad$ |                                                                    |                                                                 | 外觀               | 次要                      |                         |

|      | 點類(一)                     | $\varphi = \frac{(X + Y)}{2}$                                                                                                | 0.1 < φ<br>0.25 < φ                                                                                                                                                                                                               |                                                                    | 無視 Ignore<br>3<br>1<br>0                                        | Α                | Appearance              | Minor<br>AQL0.65%       |

| 1    | Dot (1)                   | A                                                                                                                            | The dot is log $\varphi$ $\varphi \leq 0.3 < \varphi$ $0.5 < \varphi$                                                                                                                                                             | (mm)<br>≦ 0.3<br>≦ 0.5<br>⇒ 1<br>> 1                               | side(B area)-OK<br>允收數<br>Acceptance Qty<br>無視 Ignore<br>3<br>1 | В                | 外觀<br>Appearance        | 次要<br>Minor<br>AQL0.65% |

| 2    | 點類(二)<br>Dot (2)          |                                                                                                                              | 兩點距離須超過 $5 \text{ mm}$ Two points to be $\geq 5 \text{ mm}$                                                                                                                                                                       |                                                                    | А                                                               | 外觀<br>Appearance | 次要<br>Minor<br>AQL0.65% |                         |

| 3    | 線類<br>Line                | 刮傷、毛屑等線狀<br>Scratch、Fiber and other<br>linear shape.                                                                         | L (mm) L ≦ 5 L ≦ 3 L>5                                                                                                                                                                                                            | $W \text{ (mm)}$ $W \leq 0.0$ $W \leq 0.0$ $W \leq 0.0$ $W > 0.05$ | 3 3 5 2                                                         | A                | 外觀<br>Appearance        | 次要<br>Minor<br>AQL0.65% |

| 4    | 底色<br>Background<br>color | 同批供貨不能有明顯色差 No obvious color difference allowed in same shipment. (必要時與客端制定限度樣) (According to the gold samples if necessary) |                                                                                                                                                                                                                                   |                                                                    |                                                                 | A                | 外觀<br>Appearance        | 次要<br>Minor<br>AQL0.65% |

|    |                                          |                                                                                                                                                                                                                                                             |    |                   | COB                     |

|----|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-------------------|-------------------------|

| 5  | 零件位置<br>Parts position                   | 與工程 BOM 上標示不符 拒收<br>Different with the BOM marked<br>Reject                                                                                                                                                                                                 | С  | 外觀<br>Appearance  | 主要<br>Major<br>AQL 0.4% |

| 6  | 板面潔淨<br>FPC/PCB's<br>surface is<br>clean | <ul><li>※ 焊接面上附著錫渣、珠 拒收 Solder side has tin slag, beads or particle Reject</li><li>※ 焊接面上附著於過多錫油 拒收 Solder side has too much tin oil Reject</li></ul>                                                                                                       | С  | 外觀<br>Appearance  | 次要<br>Minor<br>AQL0.65% |

| 7  | 點、線類<br>(三)<br>Dot、Line (3)              | ※ 於全黑、白畫面下看見之區塊狀或線狀不良 拒收<br>There is a block or linear in the view area under the screen is<br>whole black or white.  Reject  《 但依 2% ND Filter 遮蓋無視 允收 But after inspecting by 2% ND Filter without seeing block or<br>linear, it is confirmed  Acceptance | AA | 電訊<br>Electronics | 次要<br>Minor<br>AQL0.65% |

| 8  | 點、線類<br>(四)<br>Dot、Line (4)              | 畫面中顯示出現黑、白、亮、異色點或線狀 There is a black, white, bright or other dot or lines showing in the view area. ※ 依編號 1、3 之判定標準 According to the inspection standard: No. 1 and 3.                                                                                      | AA | 電訊<br>Electronics | 次要<br>Minor<br>AQL0.65% |

| 9  | 缺字<br>Lack of<br>characters              | 顯示時畫面缺少部份字元 拒收 Lacking part of characters in the view area. Reject                                                                                                                                                                                          | AA | 電訊<br>Electronics | 主要<br>Major<br>AQL 0.4% |

| 10 | 無動作<br>No reaction                       | 顯示畫面一直處於起始畫面而無法進行切換 拒收 The display (view area) always shows in the initial screen and can't be switched to others.  Reject                                                                                                                                  | AA | 電訊<br>Electronics | 主要<br>Major<br>AQL 0.4% |

| 11 | 無畫面<br>No display                        | 通電後,完全無任何畫面顯示 拒收<br>After connecting to the power, there is no display.<br>Reject                                                                                                                                                                           | AA | 電訊<br>Electronics | 主要<br>Major<br>AQL 0.4% |

| 12 | 斷線<br>Broken line                        | 顯示畫面中少直、橫線 拒收<br>There is a lack of vertical or horizontal lines in the view area.<br>Reject                                                                                                                                                                | AA | 電訊<br>Electronics | 主要<br>Major<br>AQL 0.4% |

| 13 | CROSS TALK                               | 顯示畫面時有局部之條紋或拖影 There are some stripes or shadow/smear showing in the view area.  拒收或與客端簽訂限度樣 Reject or inspect according to the golden sample                                                                                                               | AA | 電訊<br>Electronics | 次要<br>Minor<br>AQL0.65% |

COR

|    |                                       |                                                                                                                                                                                                                                                      |     |                                       | СОВ                     |

|----|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------------------------------------|-------------------------|

| 14 | I CON                                 | 顯示畫面缺少部份顯示圖案 拒收 Lack of partial ICON in the view area. Reject                                                                                                                                                                                        | AA  | 電訊<br>Electronics                     | 主要<br>Major<br>AQL 0.4% |

| 15 | 深淺不一<br>Color<br>difference           | 顯示畫面的對比,比其他顯示深或淺並依電氣規格(VOP)<br>值判定<br>The contrast of display is obviously lighter or darker than others<br>and according to the VOP value in the electronics specification.<br>拒收或與客端簽訂限度樣<br>Reject or inspect according to the golden sample      | AA  | 電訊<br>Electronics                     | 次要<br>Minor<br>AQL0.65% |

| 16 | 畫面異常<br>Abnormal<br>screen            | 通電後畫面出現未定義之電訊不良現象 拒收<br>After connecting to the power, there is an undefined electronics<br>appearance showing in the view area.  Reject                                                                                                             | AA  | 電訊<br>Electronics                     | 主要<br>Major<br>AQL 0.4% |

| 17 | 背光色不均<br>Uneven color of<br>backlight | <ul> <li>點亮後 LED 有明暗不均現象依其均匀度判定 拒收 After lighting LEDs have brightness and darkness uneven the determined according to its uniformity.</li> <li>Reject</li> <li>點亮後 LED 色澤不一致 拒收 LED color is inconsistent after lighting</li> <li>Reject</li> </ul> | А   | 電訊<br>Electronics                     | 次要<br>Minor<br>AQL0.65% |

| 18 | 亮度不足<br>Lack of<br>brightness         | 波長、色座標、輝度與圖面標示定義不符 拒收 Wave length, chromatic coordinates, brightness don't correspond to the definition of the drawing.  Reject                                                                                                                      | Α   | 電訊<br>Electronics                     | 次要<br>Minor<br>AQL0.65% |

| 19 | 尺寸量測<br>Size<br>Measurement           | 未依圖面上標示 拒收<br>No correspond to the indication on the drawing.<br>Reject                                                                                                                                                                              | ALL | 外觀<br>Appearance                      | 主要<br>Major<br>AQL 0.4% |

| 20 | 其他<br>Other                           | 如發現有上述未定義之不良則與客端簽訂限度樣<br>If there is another undefined defective situation. It will be listed as<br>others. The inspection standard is according to the golden sample.                                                                               | ALL | 電訊<br>Electronics<br>外觀<br>Appearance | 次要<br>Minor<br>AQL0.65% |