# **S1D15710 Series Technical Manual**

# NOTICE No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as, medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. This material or portions thereof may contain technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade Law of Japan and may require an export license from the Ministry of International Trade and Industry or other approval from another government agency. All other product names mentioned herein are trademarks and/or registered trademarks of their respective companies.

# S1D15710 Series Technical Manual

### **NOTICE**

No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind aristing out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as, medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. This material or portions thereof may contain technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade Law of Japan and may require an export licence from teh Ministry of International Trade and Industry or other approval from another government agency.

All other product names mentioned herein are trademark and/or registered trademarks of their respective companies.

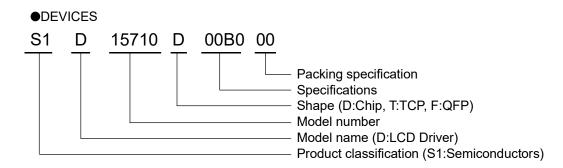

# **Configuration of product number**

### **Contents**

| 1.  | DESCRIPTION                               | 1  |

|-----|-------------------------------------------|----|

| 2.  | FEATURES                                  | 1  |

| 3.  | BLOCK DIAGRAM                             | 2  |

| 4.  | PIN LAYOUT                                | 3  |

| 5.  | PIN DESCRIPTION                           | 7  |

| 6.  | FUNCTION DESCRIPTION                      | 11 |

| 7.  | COMMAND DESCRIPTION                       | 29 |

| 8.  | COMMAND SETTING                           | 40 |

| 9.  | ABSOLUTE MAXIMUM RATINGS                  | 44 |

| 10. | DC CHARACTERISTICS                        | 45 |

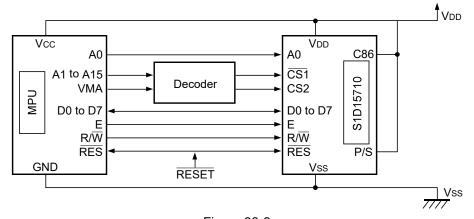

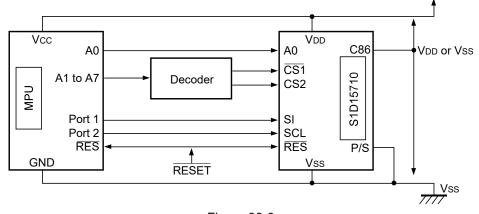

| 11. | MICROPROCESSOR (MPU) INTERFACE: REFERENCE | 57 |

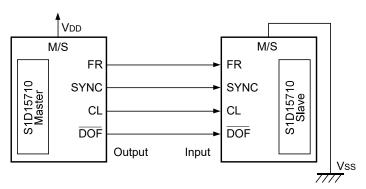

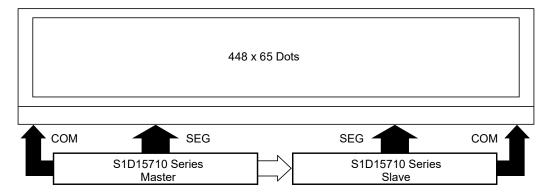

| 12. | CONNECTION BETWEEN LCD DRIVERS: REFERENCE | 58 |

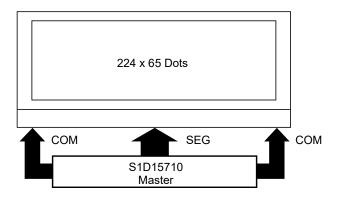

| 13. | LCD PANEL WIRING: REFERENCE               | 59 |

|     | TCP PIN LAYOUT                            |    |

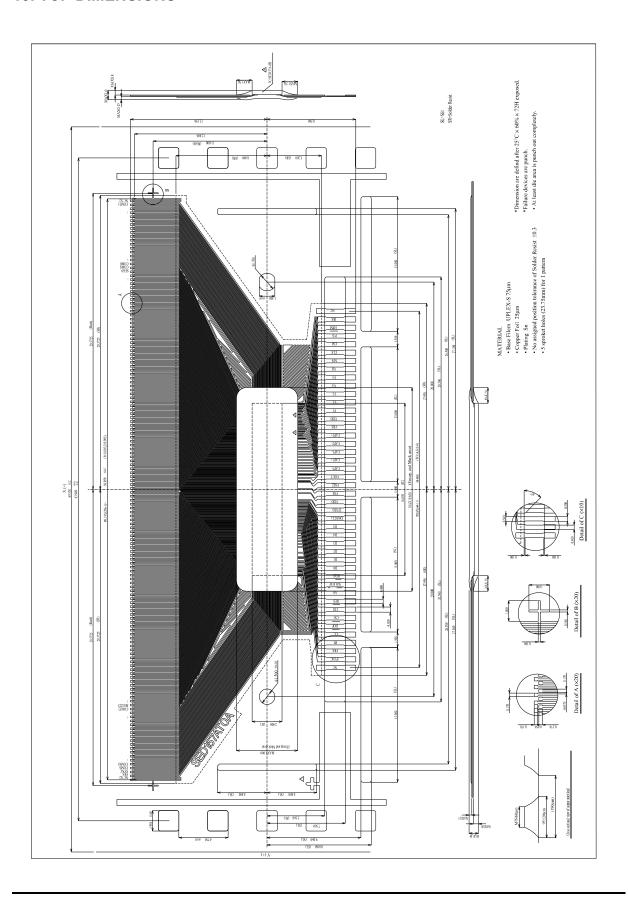

| 15. | TCP DIMENSIONS                            | 61 |

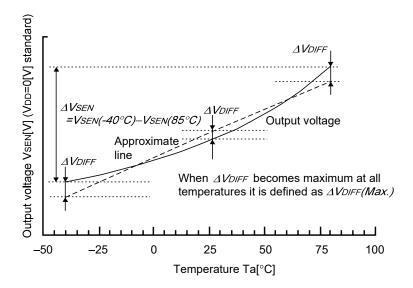

| 16. | TEMPERATURE SENSOR CIRCUIT                | 62 |

| 17  | NOTES                                     | 65 |

i

### 1. DESCRIPTION

The S1D15710 Series is a single-chip dot matrix liquid crystal display driver that can be connected directly to a microprocessor bus. Eight-bit parallel or serial display data transmitted from the microprocessor is stored in the internal display data RAM, and the chip generates liquid crystal drive signals, independently of the microprocessor.

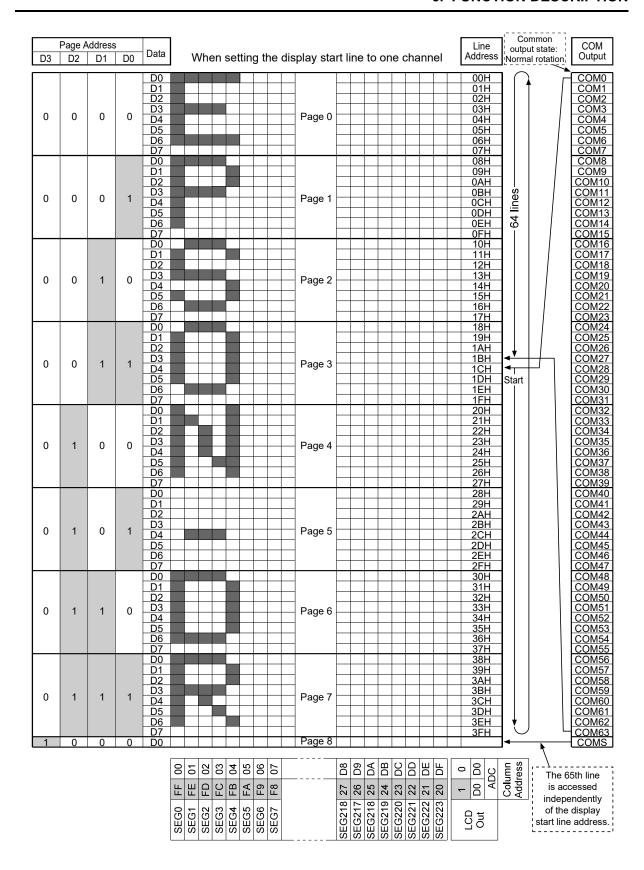

It has a on-chip  $65 \times 256$ -bit display data RAM, and there is a one-to-one correspondence between the dot pixel on the liquid crystal panel pixels and internal RAM bit. This feature ensures implementation of highly free display.

The S1D15710 Series incorporate 65 common output circuits and 224 segment output circuits. A single chip can drive a  $65 \times 224$  dot display (capable of displaying 14 columns  $\times$  4 rows with  $16 \times 16$ -dot kanji font). Further, display capacity can be extended by designing two chips in a master/display configuration.

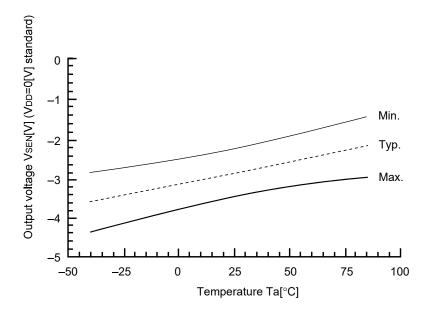

Since both the S1D15710\*10\*\* and S1D15710\*11\*\* have built-in analog temperature sensor circuits, systems can be build that can maintain appropriate liquid crystal contrast over a wide temperature range with microcomputer control without requiring such parts as thermostats.

The S1D15710 Series can read and write RAM data with the minimum current consumption because it does not require any external operation clock. Also it incorporates a LCD power supply featuring a very low current consumption, a LCD drive power voltage regulator resistor and a display clock CR oscillator circuit. This allows the display system of a high-performance for handy equipment to be realized at the minimum power consumption and minimum component configuration.

### 2. FEATURES

Direct display of RAM data using the display data RAM

RAM bit data "1" .... goes on.

"0" .... goes off (at display normal rotation).

· RAM capacity

- $65 \times 256 = 16,640$  bits

- Liquid crystal drive circuit

65 circuits for the common output and 224 circuits for the segment output

- High-speed 8-bit MPU interface (Both the 80 and 68 series MUPs can directly be connected.)/serial interface enabled

- Abundant command functions

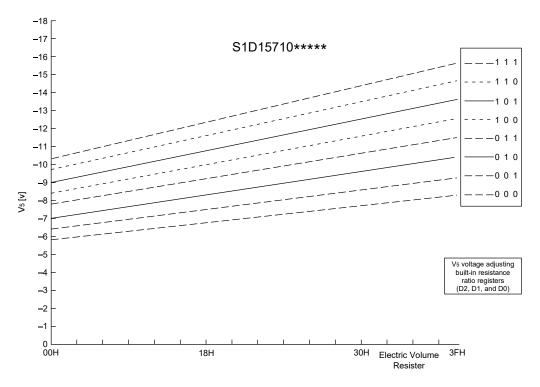

Display Data Read/Write, Display ON/OFF, Display Normal Rotation/Reversal, Page Address Set, Display Start Line Set, column address set, Status Read, Power Supply Save Display All Lighting ON/OFF, LCD Bias Set, Read Modify Write, Segment Driver Direction Select, Electronic Control, V5 Voltage Adjusting Built-in Resistance Ratio Set, Static Indicator, n Line Alternating Current Reversal Drive, Common Output State Selection, and Built-in Oscillator Circuit ON

- Built-in static drive circuit for indicators (One set, blinking speed variable)

- Built-in power supply circuit for low power supply liquid crystal drive

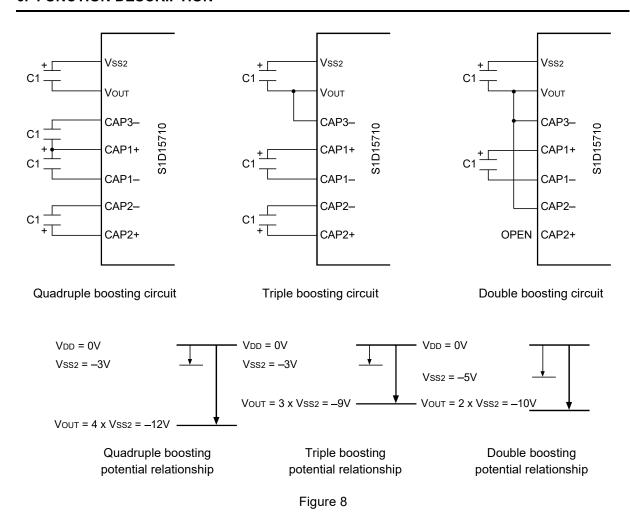

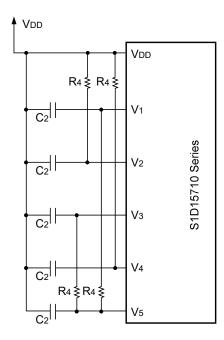

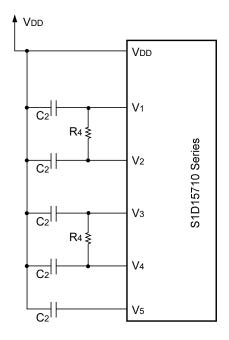

Booster circuit (Boosting magnification - double, triple, quadruple, boosting reference power supply external input enabled)

- 3% high accuracy alternating current voltage adjusting circuit (Temperature gradient: -0.05%/°C) Built-in V5 voltage adjusting resistor, built-in V1 to V4 voltage generation split resistors, built-in electronic control function, and voltage follower

- Built-in CR oscillator circuit (external clock input enabled)

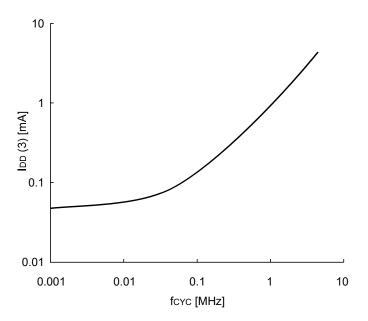

- Low power consumption

- Built-in temperature sensor circuit (S1D15710D10B\* and S1D15710D11B\*)

- Power supplies

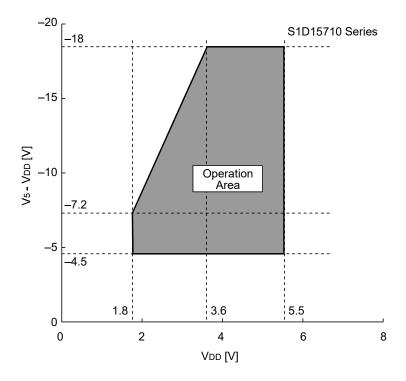

Logic power supply: VDD - VSS = 1.8 to 5.5 V Boosting reference power supply: VDD - VSS = 1.8 to 6.0 V

Liquid crystal drive power supply:  $V_5 - V_{DD} = -4.5$  to -18.0 V

- Wide operating temperature range −40 to +85°C

- · CMOS process

- Shipping form Bare chip, TCP

- No light-resistant and radiation-resistant design are provided.

### **Series specification**

| Product name      | Duty | Bias     | SEG Dr | COM Dr | VREG temperature gradient | Shipping form |

|-------------------|------|----------|--------|--------|---------------------------|---------------|

| S1D15710D00B*     | 1/65 | 1/9, 1/7 | 224    | 65     | –0.05%/°C                 | Bare chip     |

| S1D15710D10B*(*1) | 1/65 | 1/9, 1/7 | 224    | 65     | –0.05%/°C                 | Bare chip     |

| S1D15710D11B*(*2) | 1/65 | 1/9, 1/7 | 224    | 65     | –0.05%/°C                 | Bare chip     |

| S1D15710T00**     | 1/65 | 1/9. 1/7 | 224    | 65     | -0.05%/°C                 | TCP           |

- \*1: The built-in power circuit has been upgraded so that liquid crystal displays having big load capacities can be driven. Check the display and select if the display quality is inadequate even in high power mode of S1D15710D00B\*. There are no methods for supplying liquid crystal drive power externally without using the built-in power circuit. In that case, select either the S1D15710D00B\* or the S1D15710D11B\*.

- \*2: All specificationa are same as those of the S1D15710D00B\* except for the temperature sensor circuit.

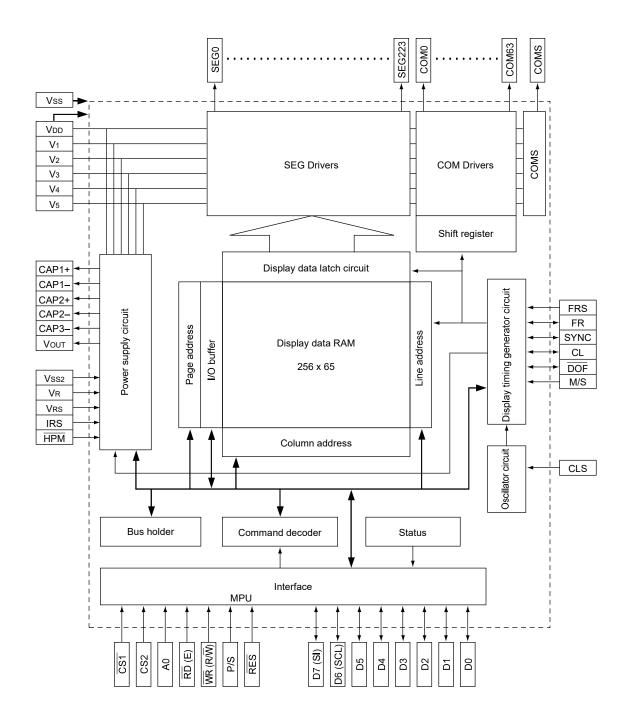

### 3. BLOCK DIAGRAM

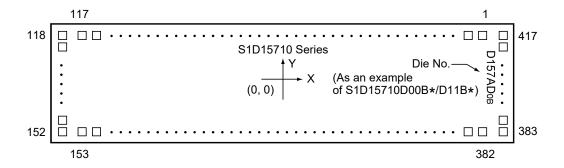

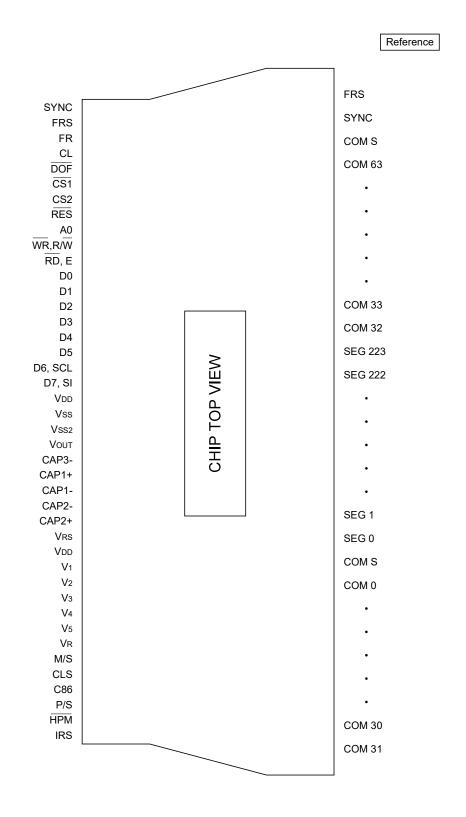

### **4. PIN LAYOUT**

### **Chip Specification**

|              | Item              | х     | Size      | Υ    | Unit |

|--------------|-------------------|-------|-----------|------|------|

| Chip size    |                   | 16.65 | ×         | 2.90 | mm   |

| Chip thickne | ess               |       | 0.625     |      | mm   |

| Bump pitch   |                   |       | 69 (Min.) | )    | μm   |

| Bump size    | PAD No.1 to 117   | 85    | ×         | 85   | μm   |

|              | PAD No.118        | 85    | ×         | 73   | μm   |

|              | PAD No.119 to 151 | 85    | ×         | 47   | μm   |

|              | PAD No.152        | 85    | ×         | 73   | μm   |

|              | PAD No.153        | 73    | ×         | 85   | μm   |

|              | PAD No.154 to 381 | 47    | ×         | 85   | μm   |

|              | PAD No.382        | 73    | ×         | 85   | μm   |

|              | PAD No.383        | 85    | ×         | 73   | μm   |

|              | PAD No.384 to 416 | 85    | ×         | 47   | μm   |

|              | PAD No.417        | 85    | ×         | 73   | μm   |

| Bump heigh   | t                 |       | 17 (Typ.  | )    | μm   |

### **PAD Central Coordinates**

Unit: µm

|   | AD<br>o. | PIN<br>Name | х            | Υ    | PAD<br>No. | PIN<br>Name | Х                                    | Υ    | PAD<br>No. | PIN<br>Name    | х                 | Υ                |

|---|----------|-------------|--------------|------|------------|-------------|--------------------------------------|------|------------|----------------|-------------------|------------------|

|   | 1        | (NC)        | 7814         | 1293 | 51         | VDD         | 972                                  | 1293 | 101        | VDD            | -5723             | 1293             |

|   | 2        | SYNC        | 7677         | 1233 | 52         | VDD         | 838                                  | 1233 | 102        | M/S            | _5859             | 1233             |

|   | 3        | FRS         | 7541         |      | 53         | VDD         | 704                                  |      | 103        | CLS            | <b>-</b> 5996     |                  |

|   | 4        | TEST1       | 7404         |      | 54         | VDD         | 571                                  |      | 104        | Vss            | <del>-</del> 6132 |                  |

|   | 5        | VDD         | 7268         |      | 55         | VDD         | 437                                  |      | 105        | C86            | <b>–</b> 6269     |                  |

|   | 6        | TEST2       | 7131         |      | 56         | Vss         | 303                                  |      | 106        | P/S            | <del>-6405</del>  |                  |

|   | 7        | Vss         | 6995         |      | 57         | Vss         | 169                                  |      | 107        | VDD            | -6542             |                  |

|   | 8        | TEST3       | 6855         |      | 58         | Vss         | 35                                   |      | 108        | HPM            | -6678             |                  |

|   | 9        | VDD         | 6718         |      | 59         | Vss2        | <b>-</b> 99                          |      | 109        | Vss            | -6815             |                  |

|   | 0        | TEST4       | 6582         |      | 60         | Vss2        | -233                                 |      | 110        | IRS            | -6951             |                  |

|   | 1        | Vss         | 6445         |      | 61         | Vss2        | -367                                 |      | 111        | VDD            | -7088             |                  |

|   | 2        | Vss         | 6309         |      | 62         | Vss2        | -501                                 |      | 112        | TEST12         | -7224             |                  |

|   | 3        | Vss         | 6169         |      | 63         | Vss2        | -635                                 |      | 113        | TEST13         | -7361             |                  |

|   | 4        | Vdd         | 6033         |      | 64         | (NC)        | -768                                 |      | 114        | TEST14         | <del>-7510</del>  |                  |

|   | 5        | Vdd         | 5896         |      | 65         | Ùουτ        | -902                                 |      | 115        | TEST15         | -7630             |                  |

| 1 | 6        | Vdd         | 5760         |      | 66         | Vout        | -1036                                |      | 116        | TEST16         | -7750             |                  |

| 1 | 7        | Vdd         | 5623         |      | 67         | CAP3-       | -1170                                |      | 117        | (NC)           | -7869             | +                |

| 1 | 8        | TEST5       | 5483         |      | 68         | CAP3-       | -1304                                |      | 118        | (NC)           | -8148             | 1295             |

| 1 | 9        | TEST5       | 5347         |      | 69         | (NC)        | _1438                                |      | 119        | COM31          |                   | 1209             |

|   | 0.       | TEST6       | 5210         |      | 70         | CAP1+       | -1572                                |      | 120        | COM30          |                   | 1137             |

|   | 1        | TEST6       | 5074         |      | 71         | CAP1+       | -1706                                |      | 121        | COM29          |                   | 1064             |

|   | 2        | TEST7       | 4937         |      | 72         | CAP1-       | -1840                                |      | 122        | COM28          |                   | 991              |

|   | 23       | TEST7       | 4798         |      | 73         | CAP1-       | -1974                                |      | 123        | COM27          |                   | 919              |

|   | 4        | TEST8       | 4661         |      | 74         | CAP2-       | -2107                                |      | 124        | COM26          |                   | 846              |

|   | 25       | TEST8       | 4525         |      | 75         | CAP2-       | -2241                                |      | 125        | COM25          |                   | 773              |

|   | 6        | TEST9       | 4388         |      | 76         | CAP2+       | -2375                                |      | 126        | COM24          |                   | 701              |

|   | 7        | TEST9       | 4252         |      | 77         | CAP2+       | -2509                                |      | 127        | COM23          |                   | 628              |

|   | 8        | SYNC        | 4112         |      | 78         | Vss         | -2643                                |      | 128        | COM22          |                   | 555              |

|   | 9        | FRS         | 3975         |      | 79         | Vss         | -2777                                |      | 129        | COM21          |                   | 483              |

|   | 0        | FR          | 3839         |      | 80         | VRS         | -2911                                |      | 130        | COM20          |                   | 410              |

|   | 1        | CL          | 3702         |      | 81         | VRS         | -3045                                |      | 131        | COM19          |                   | 337              |

|   | 2        | DOF         | 3566         |      | 82         | VDD         | -3179                                |      | 132<br>133 | COM18          |                   | 265<br>192       |

|   | 3        | Vss<br>CS1  | 3429<br>3293 |      | 83<br>84   | Vdd<br>V1   | _3313<br>_3446                       |      | 134        | COM17<br>COM16 |                   | 119              |

|   | 5        | CS2         | 3156         |      | 85         | V1<br>V1    | <del>-3440</del><br><del>-3580</del> |      | 135        | COM16          |                   | 47               |

|   | 6        | VDD         | 3020         |      | 86         | V1<br>V2    | _3714                                |      | 136        | COM13          |                   | <del>-</del> 26  |

|   | 7        | RES         | 2883         |      | 87         | V2<br>V2    | _3848                                |      | 137        | COM14          |                   | _20<br>_99       |

|   | 8        | A0          | 2747         |      | 88         | (NC)        | <del>-3982</del>                     |      | 138        | COM12          |                   | _171             |

|   | 9        | Vss         | 2610         |      | 89         | V3          | <del>-4</del> 116                    |      | 139        | COM12          |                   | -244             |

|   | .0       | WR, R/W     | 2474         |      | 90         | V3          | <del>-4250</del>                     |      | 140        | COM10          |                   | _317             |

|   | 1        | RD,E        | 2337         |      | 91         | V4          | -4384                                |      | 141        | COM9           |                   | _389             |

|   | 2        | VDD         | 2201         |      | 92         | V4<br>V4    | <del>-4518</del>                     |      | 142        | COM8           |                   | <del>-4</del> 62 |

|   | .3       | D0          | 2064         |      | 93         | V5          | <del>-4652</del>                     |      | 143        | COM7           |                   | -535             |

|   | 4        | D1          | 1928         |      | 94         | V5          | <del>-4785</del>                     |      | 144        | COM6           |                   | <del>-</del> 607 |

|   | 5        | D2          | 1791         |      | 95         | (NC)        | <del>-4</del> 919                    |      | 145        | COM5           |                   | -680             |

|   | 6        | D3          | 1655         |      | 96         | VR          | -5053                                |      | 146        | COM4           |                   | <del>-753</del>  |

|   | .7       | D4          | 1518         |      | 97         | VDD         | <b>-</b> 5187                        |      | 147        | COM3           |                   | -825             |

|   | .8       | D5          | 1382         |      | 98         | TEST10      | -5321                                |      | 148        | COM2           |                   | -898             |

|   | .9       | D6 (SCL)    | 1245         |      | 99         | Vss         | -5455                                |      | 149        | COM1           |                   | <b>-</b> 971     |

| 5 | 0        | D7 (SI)     | 1109         | 🖊    | 100        | TEST11      | -5589                                |      | 150        | COM0           | ♦                 | -1043            |

Unit: µm

| PAD | PIN   |                   |       | PAD | PIN   |                   |          | PAD | PIN    |                  |       |

|-----|-------|-------------------|-------|-----|-------|-------------------|----------|-----|--------|------------------|-------|

| No. | Name  | X                 | Y     | No. | Name  | X                 | Υ        | No. | Name   | Х                | Y     |

| 151 | COMS  | -8148             | -1116 | 201 | SEG45 | -4579             | -1293    | 251 | SEG95  | -1127            | -1293 |

| 152 | (NC)  |                   | _1201 | 202 | SEG46 | <del>-4</del> 510 |          | 252 | SEG96  | _1058            |       |

| 153 | (NC)  | <del>-</del> 7906 | _1293 | 203 | SEG47 | <del>-444</del> 1 |          | 253 | SEG97  | -989             |       |

| 154 | (NC)  | -7823             |       | 204 | SEG48 | -4372             |          | 254 | SEG98  | -920             |       |

| 155 | (NC)  | <del>-7754</del>  |       | 205 | SEG49 | -4303             |          | 255 | SEG99  | -851             |       |

| 156 | SEG0  | -7685             |       | 206 | SEG50 | -4234             |          | 256 | SEG100 | -782             |       |

| 157 | SEG1  | -7616             |       | 207 | SEG51 | <del>-4</del> 164 |          | 257 | SEG101 | <del>-</del> 713 |       |

| 158 | SEG2  | -7547             |       | 208 | SEG52 | -4095             |          | 258 | SEG102 | -644             |       |

| 159 | SEG3  | <del>-7478</del>  |       | 209 | SEG53 | -4026             |          | 259 | SEG103 | -575             |       |

| 160 | SEG4  | <del>-7409</del>  |       | 210 | SEG54 | -3957             |          | 260 | SEG104 | <b>–</b> 506     |       |

| 161 | SEG5  | -7340             |       | 211 | SEG55 | _3888             |          | 261 | SEG105 | <del>-4</del> 37 |       |

| 162 | SEG6  | -7271             |       | 212 | SEG56 | -3819             |          | 262 | SEG106 | -368             |       |

| 163 | SEG7  | -7202             |       | 213 | SEG57 | -3750             |          | 263 | SEG107 | -299             |       |

| 164 | SEG8  | <del>-7133</del>  |       | 214 | SEG58 | -3681             |          | 264 | SEG108 | -230             |       |

| 165 | SEG9  | -7064             |       | 215 | SEG59 | -3612             |          | 265 | SEG109 | -161             |       |

| 166 | SEG10 | -6995             |       | 216 | SEG60 | -3543             |          | 266 | SEG110 | -92              |       |

| 167 | SEG11 | -6926             |       | 217 | SEG61 | _3474             |          | 267 | SEG111 | -23              |       |

| 168 | SEG12 | -6857             |       | 218 | SEG62 | -3405             |          | 268 | SEG112 | 46               |       |

| 169 | SEG13 | <b>–</b> 6788     |       | 219 | SEG63 | -3336             |          | 269 | SEG113 | 115              |       |

| 170 | SEG14 | <del>-</del> 6719 |       | 220 | SEG64 | -3267             |          | 270 | SEG114 | 184              |       |

| 171 | SEG15 | -6650             |       | 221 | SEG65 | -3198             |          | 271 | SEG115 | 253              |       |

| 172 | SEG16 | -6581             |       | 222 | SEG66 | -3129             |          | 272 | SEG116 | 322              |       |

| 173 | SEG17 | -6512             |       | 223 | SEG67 | -3060             |          | 273 | SEG117 | 391              |       |

| 174 | SEG18 | -6442             |       | 224 | SEG68 | -2991             |          | 274 | SEG118 | 461              |       |

| 175 | SEG19 | -6373             |       | 225 | SEG69 | -2922             |          | 275 | SEG119 | 530              |       |

| 176 | SEG20 | -6304             |       | 226 | SEG70 | -2853             |          | 276 | SEG120 | 599              |       |

| 177 | SEG21 | -6235             |       | 227 | SEG71 | -2784             |          | 277 | SEG121 | 668              |       |

| 178 | SEG22 | <b>–</b> 6166     |       | 228 | SEG72 | <b>–2715</b>      |          | 278 | SEG122 | 737              |       |

| 179 | SEG23 | -6097             |       | 229 | SEG73 | -2646             |          | 279 | SEG123 | 806              |       |

| 180 | SEG24 | -6028             |       | 230 | SEG74 | -2577             |          | 280 | SEG124 | 875              |       |

| 181 | SEG25 | -5959             |       | 231 | SEG75 | -2508             |          | 281 | SEG125 | 944              |       |

| 182 | SEG26 | -5890             |       | 232 | SEG76 | -2439             |          | 282 | SEG126 | 1013             |       |

| 183 | SEG27 | -5821             |       | 233 | SEG77 | -2370             |          | 283 | SEG127 | 1082             |       |

| 184 | SEG28 | <b>–</b> 5752     |       | 234 | SEG78 | -2301             |          | 284 | SEG128 | 1151             |       |

| 185 | SEG29 | -5683             |       | 235 | SEG79 | -2232             |          | 285 | SEG129 | 1220             |       |

| 186 | SEG30 | -5614             |       | 236 | SEG80 | -2163             |          | 286 | SEG130 | 1289             |       |

| 187 | SEG31 | -5545             |       | 237 | SEG81 | -2094             |          | 287 | SEG131 | 1358             |       |

| 188 | SEG32 | -5476             |       | 238 | SEG82 | -2025             |          | 288 | SEG132 | 1427             |       |

| 189 | SEG33 | -5407             |       | 239 | SEG83 | -1956             |          | 289 | SEG133 | 1496             |       |

| 190 | SEG34 | -5338             |       | 240 | SEG84 | -1886             |          | 290 | SEG134 | 1565             |       |

| 191 | SEG35 | <b>–</b> 5269     |       | 241 | SEG85 | -1817             |          | 291 | SEG135 | 1634             |       |

| 192 | SEG36 | -5200             |       | 242 | SEG86 | -1748             |          | 292 | SEG136 | 1703             |       |

| 193 | SEG37 | -5131             |       | 243 | SEG87 | -1679             |          | 293 | SEG137 | 1772             |       |

| 194 | SEG38 | -5062             |       | 244 | SEG88 | -1610             |          | 294 | SEG138 | 1841             |       |

| 195 | SEG39 | <del>-4993</del>  |       | 245 | SEG89 | -1541             |          | 295 | SEG139 | 1910             |       |

| 196 | SEG40 | <del>-4924</del>  |       | 246 | SEG90 | -1472             |          | 296 | SEG140 | 1979             |       |

| 197 | SEG41 | <del>-4855</del>  |       | 247 | SEG91 | -1403             |          | 297 | SEG141 | 2048             |       |

| 198 | SEG42 | <del>-4786</del>  |       | 248 | SEG92 | -1334             |          | 298 | SEG142 | 2117             |       |

| 199 | SEG43 | <del>-4717</del>  |       | 249 | SEG93 | -1265             |          | 299 | SEG143 | 2186             |       |

| 200 | SEG44 | <del>-4</del> 648 | ▼     | 250 | SEG94 | -1196             | <b>V</b> | 300 | SEG144 | 2255             | ▼     |

Unit: µm

|            |                  |              |       |            |                |      |                          |            |             |      | ∪nıt: µm |

|------------|------------------|--------------|-------|------------|----------------|------|--------------------------|------------|-------------|------|----------|

| PAD<br>No. | PIN<br>Name      | X            | Y     | PAD<br>No. | PIN<br>Name    | X    | Y                        | PAD<br>No. | PIN<br>Name | X    | Y        |

| 301        | SEG145           | 2324         | -1293 | 351        | SEG195         | 5776 | -1293                    | 401        | COM49       | 8148 | 119      |

| 302        | SEG146           | 2393         |       | 352        | SEG196         | 5845 | 1200                     | 402        | COM50       |      | 192      |

| 303        | SEG147           | 2462         |       | 353        | SEG197         | 5914 |                          | 403        | COM51       |      | 265      |

| 304        | SEG148           | 2531         |       | 354        | SEG198         | 5983 |                          | 404        | COM52       |      | 337      |

| 305        | SEG149           | 2600         |       | 355        | SEG199         | 6052 |                          | 405        | COM53       |      | 410      |

| 306        | SEG150           | 2669         |       | 356        | SEG200         | 6121 |                          | 406        | COM54       |      | 483      |

| 307        | SEG151           | 2739         |       | 357        | SEG201         | 6190 |                          | 407        | COM55       |      | 555      |

| 308        | SEG152           | 2808         |       | 358        | SEG202         | 6259 |                          | 408        | COM56       |      | 628      |

| 309        | SEG153           | 2877         |       | 359        | SEG203         | 6328 |                          | 409        | COM57       |      | 701      |

| 310        | SEG154           | 2946         |       | 360        | SEG204         | 6397 |                          | 410        | COM58       |      | 773      |

| 311        | SEG155           | 3015         |       | 361        | SEG205         | 6466 |                          | 411        | COM59       |      | 846      |

| 312        | SEG156           | 3084         |       | 362        | SEG206         | 6535 |                          | 412        | COM60       |      | 919      |

| 313        | SEG157           | 3153         |       | 363        | SEG207         | 6604 |                          | 413        | COM61       |      | 991      |

| 314        | SEG158           | 3222         |       | 364        | SEG208         | 6673 |                          | 414        | COM62       |      | 1064     |

| 315        | SEG159           | 3291         |       | 365        | SEG209         | 6742 |                          | 415        | COM63       |      | 1137     |

| 316        | SEG160           | 3360         |       | 366        | SEG210         | 6811 |                          | 416        | COMS        |      | 1209     |

| 317        | SEG161           | 3429         |       | 367        | SEG211         | 6880 |                          | 417        | (NC)        | ▼    | 1295     |

| 318        | SEG162           | 3498         |       | 368        | SEG212         | 6949 |                          |            |             |      |          |

| 319        | SEG163           | 3567         |       | 369        | SEG213         | 7018 |                          |            |             |      |          |

| 320        | SEG164           | 3636         |       | 370        | SEG214         | 7087 |                          |            |             |      |          |

| 321        | SEG165           | 3705         |       | 371        | SEG215         | 7156 |                          |            |             |      |          |

| 322        | SEG166           | 3774         |       | 372        | SEG216         | 7225 |                          |            |             |      |          |

| 323        | SEG167           | 3843         |       | 373        | SEG217         | 7294 |                          |            |             |      |          |

| 324        | SEG168           | 3912         |       | 374        | SEG218         | 7364 |                          |            |             |      |          |

| 325        | SEG169           | 3981         |       | 375        | SEG219         | 7433 |                          |            |             |      |          |

| 326        | SEG170           | 4050         |       | 376        | SEG220         | 7502 |                          |            |             |      |          |

| 327        | SEG171           | 4119         |       | 377        | SEG221         | 7571 |                          |            |             |      |          |

| 328        | SEG172           | 4188         |       | 378        | SEG222         | 7640 |                          |            |             |      |          |

| 329        | SEG173           | 4257         |       | 379        | SEG223         | 7709 |                          |            |             |      |          |

| 330        | SEG174           | 4326         |       | 380        | (NC)           | 7778 |                          |            |             |      |          |

| 331        | SEG175           | 4395         |       | 381        | (NC)           | 7847 |                          |            |             |      |          |

| 332        | SEG176           | 4464         |       | 382        | (NC)           | 7930 | <b>V</b>                 |            |             |      |          |

| 333        | SEG177           | 4533         |       | 383        | (NC)           | 8148 | -1201                    |            |             |      |          |

| 334        | SEG178           | 4602         |       | 384        | COM32          |      | -1116                    |            |             |      |          |

| 335        | SEG179           | 4671         |       | 385        | COM33          |      | -1043                    |            |             |      |          |

| 336        | SEG180           | 4740         |       | 386        | COM34          |      | <del>-971</del>          |            |             |      |          |

| 337        | SEG181           | 4809         |       | 387        | COM35          |      | _898<br>825              |            |             |      |          |

| 338        | SEG182           | 4878         |       | 388        | COM36          |      | -825<br>753              |            |             |      |          |

| 339        | SEG183           | 4947         |       | 389        | COM37          |      | -753                     |            |             |      |          |

| 340<br>341 | SEG184           | 5017         |       | 390        | COM38          |      | -680<br>607              |            |             |      |          |

| 341        | SEG185<br>SEG186 | 5086<br>5155 |       | 391<br>392 | COM39<br>COM40 |      | _607<br>_535             |            |             |      |          |

| 343        | SEG 180          | 5224         |       | 393        | COM40          |      | _333<br>_462             |            |             |      |          |

| 344        | SEG187           | 5293         |       | 394        | COM41          |      | <del>-4</del> 62<br>-389 |            |             |      |          |

| 345        | SEG189           | 5362         |       | 395        | COM42          |      | _309<br>_317             |            |             |      |          |

| 346        | SEG199           | 5431         |       | 396        | COM43          |      | _317<br>_244             |            |             |      |          |

| 347        | SEG190           | 5500         |       | 397        | COM44          |      | _244<br>_171             |            |             |      |          |

| 348        | SEG192           | 5569         |       | 398        | COM46          |      | _99                      |            |             |      |          |

| 349        | SEG193           | 5638         |       | 399        | COM47          |      | _35<br>_26               |            |             |      |          |

| 350        | SEG194           | 5707         | ↓     | 400        | COM48          | \    | 47                       |            |             |      |          |

| 000        | 00104            | 0,01         |       | 700        | CONTO          |      | 71                       |            |             |      |          |

### **5. PIN DESCRIPTION**

### **Power Supply Pin**

| Pin name               | I/O          | Description                                                                                                                                                                                                                                                                                                                              | Number of pins |

|------------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| VDD                    | Power supply | Commonly used with the MPU power supply pin Vcc.                                                                                                                                                                                                                                                                                         | 12             |

| Vss                    | Power supply | 0 V pin connected to the system ground (GND)                                                                                                                                                                                                                                                                                             | 9              |

| Vss2                   | Power supply | Boosting circuit reference power supply for liquid crystal drive                                                                                                                                                                                                                                                                         | 5              |

| VRS                    | Power supply | External input pin for liquid crystal power supply voltage adjusting circuit They are set to OPEN                                                                                                                                                                                                                                        | 2              |

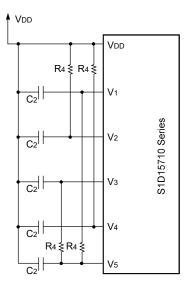

| V1, V2<br>V3, V4<br>V5 | Power supply | Multi-level power supply for liquid crystal drive. The voltage specified according to liquid crystal cells is impedance-converted by a split resistor or operation amplifier (OP amp) and applied. The potential needs to be specified based on VDD to establish the relationship of dimensions shown below:                             | 10             |

|                        |              | VDD (=V0) $\geq$ V1 $\geq$ V2 $\geq$ V3 $\geq$ V4 $\geq$ V5  Master operation When the power supply is ON, the following voltages are applied to V1 $\sim$ V4 from the built-in power supply circuit. The selection of the voltages is determined using the LCD bias set command. $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ |                |

### **LCD Power Supply Circuit Pin**

| Pin name | I/O | Description                                                                                                                                                                                | Number of pins |

|----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| CAP1+    | 0   | Boosting capacitor positive side connecting pin. Connects a capacitor between the pin and CAP1– pin.                                                                                       | 2              |

| CAP1-    | 0   | Boosting capacitor negative side connecting pin. Connects a capacitor between the pin and CAP1+ pin.                                                                                       | 2              |

| CAP2+    | 0   | Boosting capacitor positive side connecting pin. Connects a capacitor between the pin and CAP2– pin.                                                                                       | 2              |

| CAP2-    | 0   | Boosting capacitor negative side connecting pin. Connects a capacitor between the pin and CAP2+ pin.                                                                                       | 2              |

| CAP3-    | 0   | Boosting capacitor negative side connecting pin. Connects a capacitor between the pin and CAP1+ pin.                                                                                       | 2              |

| Vout     | I/O | Boosting output pin. Connects a capacitor between the pin and Vss2.                                                                                                                        | 2              |

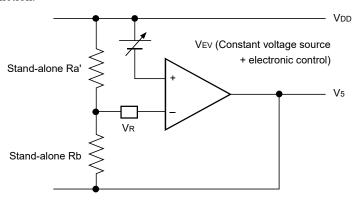

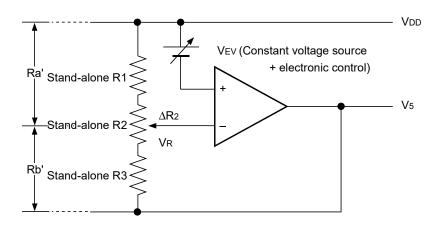

| VR       | I   | Voltage adjusting pin. Applies voltage between VDD and V5 using a split resistor.                                                                                                          | 1              |

|          |     | Valid only when the V <sub>5</sub> voltage adjusting built-in resistor is not used (IRS=LOW)  Do not use VR when the V <sub>5</sub> voltage adjusting built-in resistor is used (IRS=HIGH) |                |

## **System Bus Connecting Pins**

| Pin name                                                                                                                                                                                         | I/O |                                                                 |                                                                                                                                                                                                                                                                                                                                             | Description                                                            | on                                                        |                                    | Number of pins |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|-----------------------------------------------------------|------------------------------------|----------------|--|--|

| D7 to D0<br>(SI)<br>(SCL)                                                                                                                                                                        | I/O | standard<br>When the<br>D7: Ser<br>D6: Ser<br>In this cas       | MPU data but serial interfacial data entry ial clock inpuse, D0 to D5 ip Select is in                                                                                                                                                                                                                                                       | us.<br>ace is selected<br>y pin (SI)<br>ut pin (SCL)<br>are set to hig | ed to connect a d (P/S=LOW), h impedance. ve state, D0 to | n 8-bit or 16-bit<br>D7 are set to | 8              |  |  |

| A0                                                                                                                                                                                               | I   | to discrim                                                      | Normally the lowest order bit of the MPU address bus is connected to discriminate data / commands.  A0=HIGH: Indicates that D0 to D7 are display data.  A0=LOW: Indicates that D0 to D7 are control data.                                                                                                                                   |                                                                        |                                                           |                                    |                |  |  |

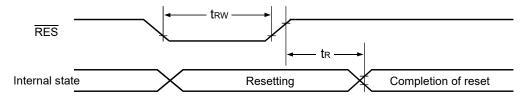

| RES                                                                                                                                                                                              | I   |                                                                 | nitialized by setting RES to LOW. Reset operation is performed at the RES signal level.                                                                                                                                                                                                                                                     |                                                                        |                                                           |                                    |                |  |  |

| CS1<br>CS2                                                                                                                                                                                       | I   |                                                                 |                                                                                                                                                                                                                                                                                                                                             |                                                                        | V and CS2=HI0<br>t of data/comm                           | GH, this signal ands is enabled.   | 2              |  |  |

| RD<br>(E)                                                                                                                                                                                        | I   | Pin that signal is • When th                                    | <ul> <li>When the 80 series MPU is connected, active LOW is set.</li> <li>Pin that connects the RD signal of the 80 series MPU. When this signal is LOW, the S1D15710 series data bus is set in the output state</li> <li>When the 68 series MPU is connected, active HIGH is set.</li> <li>68 series MPU enable clock input pin</li> </ul> |                                                                        |                                                           |                                    |                |  |  |

| WR<br>(R/W)                                                                                                                                                                                      | I   | Pin that<br>bus sign<br>• When th<br>Read/wi<br>R/ <u>W</u> =HI | <ul> <li>When the 80 series MPU is connected, active LOW is set. Pin that connects the WR signal of the 80 series MPU. The data bus signal is latched on the leading edge of the WR signal.</li> <li>When the 68 series MPU is connected, Read/write control signal input pin R/W=HIGH: Read operation R/W=LOW: Write operation</li> </ul>  |                                                                        |                                                           |                                    |                |  |  |

| FRS                                                                                                                                                                                              | 0   |                                                                 | n for static di                                                                                                                                                                                                                                                                                                                             |                                                                        |                                                           |                                    | 1              |  |  |

| C86                                                                                                                                                                                              | I   | C86=HI                                                          |                                                                                                                                                                                                                                                                                                                                             | ng pin<br>es MPU interfa<br>s MPU interfa                              |                                                           |                                    | 1              |  |  |

| P/S                                                                                                                                                                                              | I   | P/S=HIGI<br>P/S=LOW                                             | H: Parallel da<br>/: Serial data                                                                                                                                                                                                                                                                                                            | ata entry<br>a entry                                                   | /serial data enti                                         |                                    | 1              |  |  |

|                                                                                                                                                                                                  |     | P/S                                                             | Data/<br>command                                                                                                                                                                                                                                                                                                                            | Data                                                                   | Read/write                                                | Serial clock                       |                |  |  |

|                                                                                                                                                                                                  |     | HIGH                                                            | A0                                                                                                                                                                                                                                                                                                                                          | D0 to D7                                                               | RD, WR                                                    |                                    |                |  |  |

|                                                                                                                                                                                                  |     | LOW                                                             |                                                                                                                                                                                                                                                                                                                                             |                                                                        |                                                           |                                    |                |  |  |

| When P/S=LOW, D0 to D5 are set to high impedance. D0 to D5 can be HIGH, LOW, or "OPEN". RD(E) and WR (R/W) are fixed to HIGH or LOW. For the serial data entry, RAM display data cannot be read. |     |                                                                 |                                                                                                                                                                                                                                                                                                                                             |                                                                        |                                                           |                                    |                |  |  |

| Pin name | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Number of pins |

|----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| CLS      | I   | Pin that selects the validity/invalidity of the built-in oscillator circuit for display clocks.  CLS=HIGH: Built-in oscillator circuit valid CLS=LOW: Built-in oscillator circuit invalid (external input) When CLS=LOW, display clocks are input from the CL pin. When the S1D15710 series is used for the master/slave configuration, each of the CLS pins is set to the same level together.  Display clock  Built-in oscillator circuit used HIGH HIGH External input LOW LOW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1              |

| M/S      | I   | Pin that selects the master/slave operation for the S1D15710 series. The liquid crystal display system is synchronized by outputting the timing signal required for the liquid crystal display for the master operation and inputting the timing signal required for the liquid crystal display for the slave operation.  M/S=HIGH: Master operation  M/S=LOW: Slave operation  According to the M/S and CLS states, the following table is given.  M/S CLS Oscillator Power supply CL FR SYNC FRS DOF circuit circuit  HIGH HIGH Valid Valid Output Output Output Output LOW Invalid Valid Input Output Outpu | 1              |

|          |     | LOW HIGH Invalid Invalid Input Input Input Output Input LOW Invalid Invalid Input In |                |

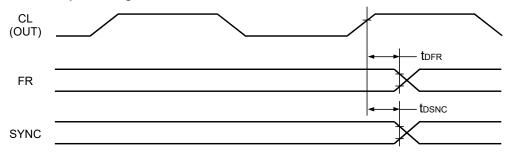

| CL       | I/O | Display clock I/O pin According to the M/S and CLS states, the following table is given.  M/S CLS CL HIGH HIGH Output LOW Input LOW Input LOW Input When the S1D15710 series is used for the master/slave configuration, each CL pin is connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1              |

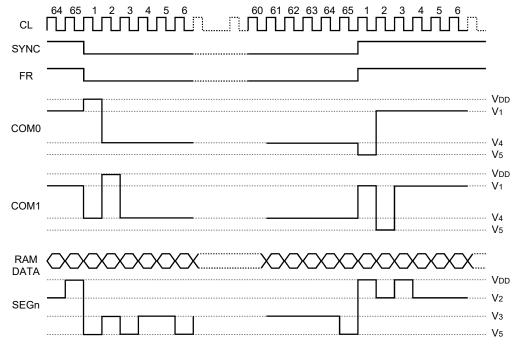

| FR       | I/O | Liquid crystal alternating current signal I/O pin M/S=HIGH: Output M/S=LOW: Input When the S1D15710 series is used for the master/slave configuration, each FR pin is connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1              |

| SYNC     | I/O | Liquid crystal synchronizing current signal I/O pin M/S=HIGH: Output M/S=LOW: Input When the S1D15710 series is used for the master/slave configuration, each SYNC pin is connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2              |

| DOF      | I/O | Liquid crystal display blanking control pin M/S=HIGH: Output M/S=LOW: Input When the S1D15710 series is used for the master/slave configuration, each DOF pin is connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1              |

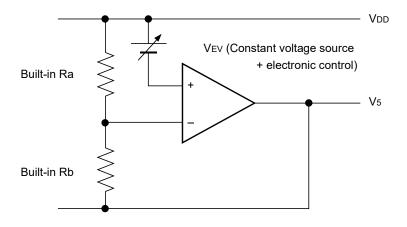

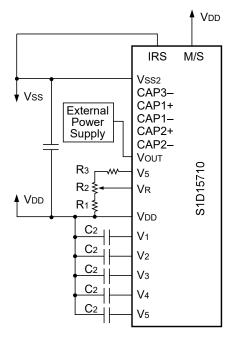

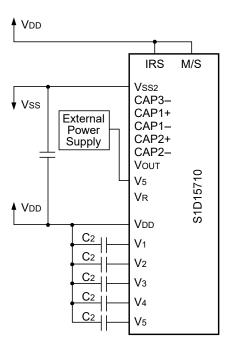

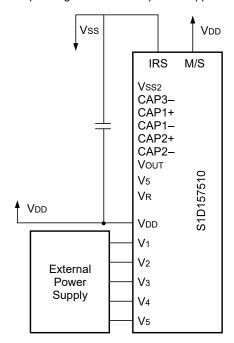

| IRS      | I   | V5 voltage adjusting resistor selection pin IRS=HIGH: Built-in resistor used IRS=LOW: Built-in resistor not used. The V5 voltage is adjusted by the VR pin and stand-alone split resistor. Valid only at master operation. The pin is fixed to HIGH or LOW at slave operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1              |

| НРМ      | I   | Power supply control pin of the power supply circuit for liquid crystal drive HPM=HIGH: Normal mode HPM=LOW: High power supply mode Valid only at master operation. The pin is fixed to HIGH or LOW at slave operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1              |

### 5. PIN DESCRIPTION

### **Liquid Crystal Drive Pin**

| Pin name             | I/O |                                                                           | Description             |                                              |                                           |     |  |  |  |  |

|----------------------|-----|---------------------------------------------------------------------------|-------------------------|----------------------------------------------|-------------------------------------------|-----|--|--|--|--|

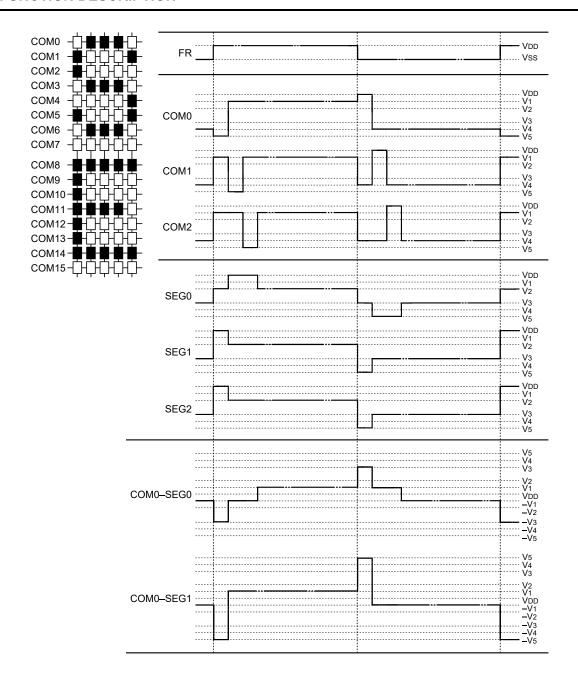

| SEG0<br>to<br>SEG223 | 0   | Output pins for the RAM and FR sig                                        | nal are co              | egment drive. Conte<br>ombined to select a d | nts of the display<br>lesired level among | 224 |  |  |  |  |

|                      |     |                                                                           |                         | Output                                       | voltage                                   |     |  |  |  |  |

|                      |     | RAM data                                                                  | FR                      | Display normal operation                     | Display reversal                          |     |  |  |  |  |

|                      |     | HIGH                                                                      | HIGH                    | VDD                                          | V2                                        |     |  |  |  |  |

|                      |     | HIGH                                                                      | LOW                     | V5                                           | V3                                        |     |  |  |  |  |

|                      |     | LOW                                                                       | HIGH                    | V2                                           | VDD                                       |     |  |  |  |  |

|                      |     | LOW                                                                       | LOW                     | V3                                           | V5                                        |     |  |  |  |  |

|                      |     | Power save                                                                |                         | Vı                                           | DD                                        |     |  |  |  |  |

| COM0<br>to<br>COM63  |     | Output pins for the are combined to                                       | he LCD co<br>select a c | ommon drive. Scan desired level among \      | data and FR signal<br>VDD, V1, V4 and V5. | 64  |  |  |  |  |

|                      |     | Scanning of                                                               | data                    | FR                                           | Output voltage                            |     |  |  |  |  |

|                      |     | HIGH                                                                      |                         | HIGH                                         | V5                                        |     |  |  |  |  |

|                      |     | HIGH                                                                      |                         | LOW                                          | VDD                                       |     |  |  |  |  |

|                      |     | LOW                                                                       |                         | HIGH                                         | V1                                        |     |  |  |  |  |

|                      |     | LOW                                                                       |                         | LOW                                          | V4                                        |     |  |  |  |  |

|                      |     | Power sa                                                                  | ve                      | _                                            | VDD                                       |     |  |  |  |  |

| COMS                 | 0   | Indicator dedicat<br>Set to OPEN wh<br>When COMS is<br>signal is output t | 2                       |                                              |                                           |     |  |  |  |  |

### **Test Pin**

| Pin name                | I/O | Description                                                                                                                               | Number of pins |

|-------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| TEST1 to 4              | I/O | Fix the pin to HIGH. To use a built-in temperature sensor circuit in the S1D15710*00**/S1D15710*11**, see 16, Temperature Sensor Circuit. | 4              |

| TEST10                  | I   | Fix it to HIGH for the S1D15710*00**/S1D15710*11**; fix it to LOW for S1D15710*10**.                                                      | 1              |

| TEST11to13              | I/O | IC chip test pin. Fix the pin to HIGH.                                                                                                    | 3              |

| TEST5 to 9,<br>14 to 16 | I/O | IC chip test pin. Take into consideration so that the capacity of lines cannot be exhausted by setting the pin to OPEN.                   | 13             |

### 6. FUNCTION DESCRIPTION

### **MPU Interface**

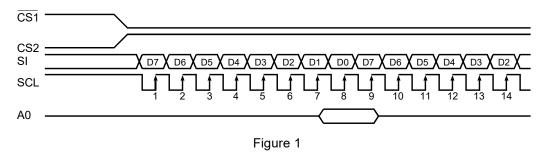

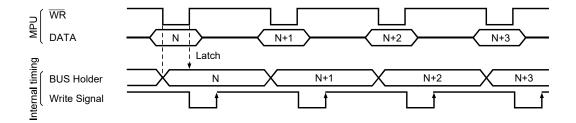

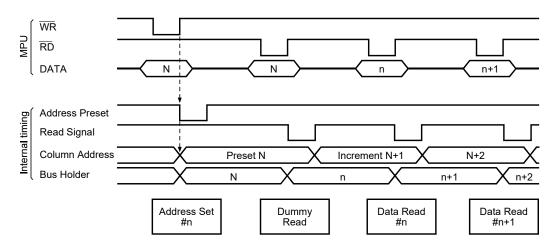

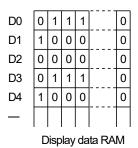

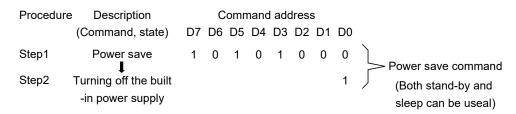

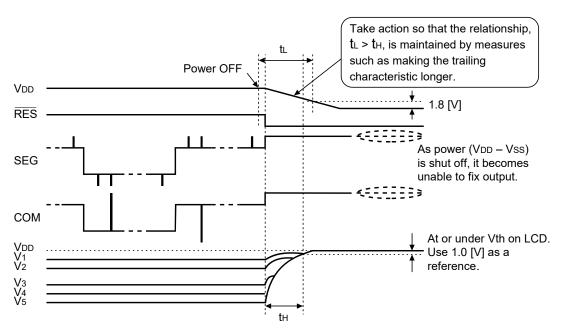

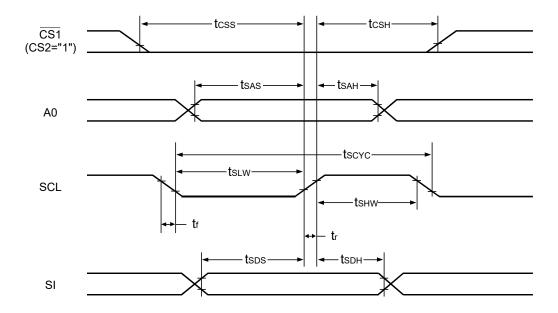

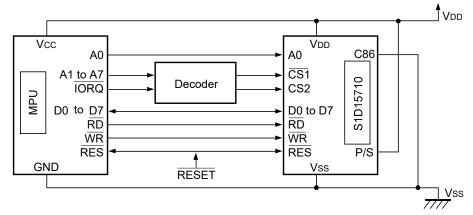

### Selection of interface type