# AK5406 80MSPS Triple ADC for Displays

# **General Description**

The AK5406 is an RGB Graphic & D-terminal Signal Process Device in which integrates 10-Bit 80Mhz AD Converters.

The Device has On-Chip 3 Channels ADCs, Voltage Reference circuit, Programmable Gain Offset Amplifiers and Black Loop Function which automatically sustains Clamp Level to an arbitrarily set value.

## Features

•

- ADCs 80 MSPS max. (Internally 10-bit, Output is reduced to 8-bit)

- $0.5V \sim 1.0V$  input signal range

- Black Loop (Automatic Offset adjust) function

- Low Clock Jitter

- On-Chip SYNC Separation function

- Pedestal Clamp and Mid-Point Clamp function

- AVDD AVSS PVDD BIAS BYPASS DVDD DVSS ----------VREF 1010bit BLACK ROUT7~0 RIN [ CLAMP PGA ADC LOOP 8 The same as Rch GOUT7~0 GIN [ 8 The same as Rch BIN [ BOUT7~0 CLAMP[ DTCLK COAST Sync Processing SOGIN SOGOUT VSYNC [ VSYNCO HSYNC<sup>[</sup> HSYNCO TEST2 [ Control Serial I/F FLT TEST SDA SCL A0 RESET

- Fig. 1 Block Diagram

- MS0592-E-01

- Power Down function

- Low Power Dissipation

- $3.3V \pm 0.3V$  power supply

- CMOS

- -40°C to 85°C

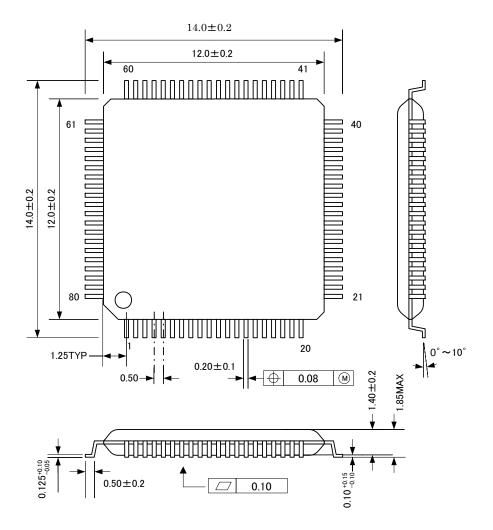

- Package 80-LQFP

#### Functional Block Description Table 1 : Block Description

|                    | k Description |                                                            |  |  |  |  |

|--------------------|---------------|------------------------------------------------------------|--|--|--|--|

| block              |               | Function                                                   |  |  |  |  |

| CLAMP              | To Clamp Pe   | edestal level of input signal during Clamp period.         |  |  |  |  |

| PGA                | Programmab    | ole Gain Amplifier.                                        |  |  |  |  |

|                    |               | resolution. Full-scale input range of ADC can be           |  |  |  |  |

|                    | pre-set from  | 0.5V to 1V.                                                |  |  |  |  |

| ADC                | 10-bit 80 MS  | SPS AD Converter.                                          |  |  |  |  |

| BLACK LOOP         | A loop to set | tle Pedestal level to the Black set value.                 |  |  |  |  |

|                    | Can be disab  | le by register setting.                                    |  |  |  |  |

| VREF               | To generate   | To generate internal reference voltage.                    |  |  |  |  |

| Control Serial I/F | Control regis | Control register with I <sup>2</sup> C Interface (400KHz). |  |  |  |  |

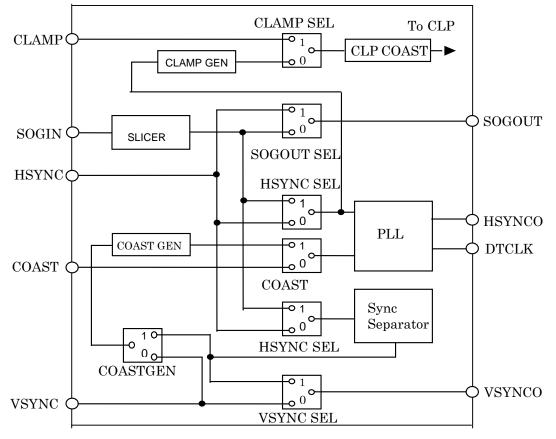

| Sync Processing    | To generate   | timing signals such as ADC operating clock, from           |  |  |  |  |

|                    | Horizontal /  | Vertical SYNC signal inputs.                               |  |  |  |  |

|                    | SLICER        | Comparator to slice SYNC signal part in                    |  |  |  |  |

|                    |               | SYNC-ON-Green signal.                                      |  |  |  |  |

|                    | PLL           | PLL to generate Pixel Clock from Horizontal SYNC           |  |  |  |  |

|                    |               | signal                                                     |  |  |  |  |

|                    | COAST         | To generate Coast signal from VSYNC.                       |  |  |  |  |

|                    | GEN           |                                                            |  |  |  |  |

|                    | CLAMP         | To generate Clamp signal from HSYNC.                       |  |  |  |  |

|                    | GEN           |                                                            |  |  |  |  |

|                    | CLP           | To execute Coast processing on Clamp signal.               |  |  |  |  |

|                    | ~ ~ . ~ ~ ~   |                                                            |  |  |  |  |

|                    | COAST         |                                                            |  |  |  |  |

Fig. 2 Sync Processing

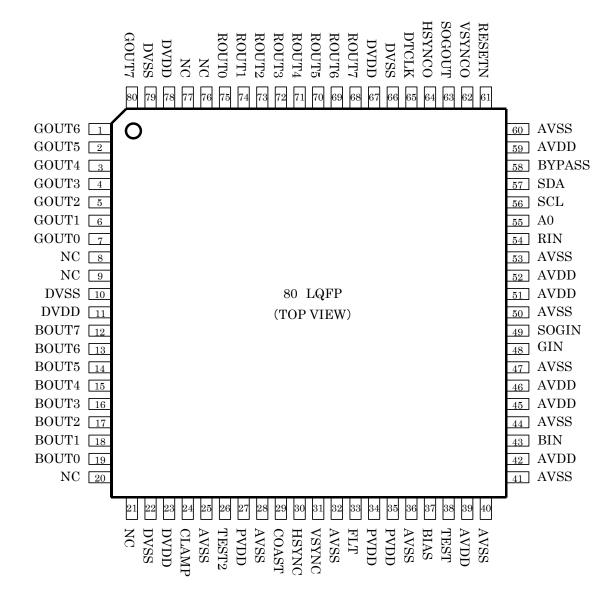

Pin Allocations

# ■ Pin Functions

Table 2 : Pin Functions

| 140        | Din nome                     | I/O  | Functions                                                   |

|------------|------------------------------|------|-------------------------------------------------------------|

| <u> </u>   | Pin name                     | 1/0  | Functions                                                   |

| Output     | Pins                         |      |                                                             |

| 64         | HSYNCO                       | DO   | Horizontal SYNC output.                                     |

|            |                              |      | HSYNC output which is re-configured HSYNC input signal      |

|            |                              |      | by internal timing.                                         |

|            |                              |      | It is phase-synchronized with DTCLK. When phase of          |

|            |                              |      | DTCLK is modified by Clock Phase Adjust register setting,   |

|            |                              |      | this output phase also changes in sync with it.             |

| 62         | VSYNCO                       | DO   | Vertical SYNC output.                                       |

|            |                              |      | Either VSYNC input or Sync Separator could be output.       |

| 63         | SOGOUT                       | DO   | Sync-On-Green Slice comparator output.                      |

|            | Interface (I <sup>2</sup> C) |      | Sync On Green Since comparator output.                      |

|            |                              |      |                                                             |

| 57         | SDA                          | DI/  | Data I/O pins                                               |

|            | ~~~                          | DO   |                                                             |

| 56         | SCL                          | DI   | Clock                                                       |

| 55         | AO                           | DI   | Address                                                     |

| 61         | RESETN                       | DI   | Register initialization signal input ( active low ).        |

| Data P     |                              |      |                                                             |

| 68         | ROUT7                        | DO   | RED channel ADC outputs                                     |

| ~75        | ~ROUT0                       |      |                                                             |

| 80,        | GOUT7                        |      | GREEN channel ADC outputs                                   |

| $1 \sim 7$ | ~GOUT0                       |      |                                                             |

| 12         | BOUT7                        |      | BLUE channels ADC outputs                                   |

| ~19        | ~BOUT0                       |      |                                                             |

|            |                              |      | Bit 7 is the MSB. They are output in sync with DTCLK.       |

|            |                              |      | When DTCLK phase is modify by Clock Adjust register         |

|            |                              |      | setting, these output phases also change in sync with it.   |

| Data C     | lock Pins                    | •    | · · · · · · · · ·                                           |

| 65         | DTCLK                        | DO   | Strobe clock for Data and HSYNCO. It is generated by PLL    |

|            |                              |      | and synchronized with internal ADC sampling clock.          |

|            |                              |      | Its phase changes in accordance with Clock Phase Adjust     |

|            |                              |      | register setting. It is phase-synchronized with HSYNCO and  |

|            |                              |      | Data.                                                       |

| Input I    | Pins                         |      |                                                             |

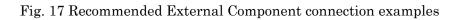

| 54         | RIN                          | AI   | RED channel analog input.                                   |

| 48         | GIN                          |      | GREEN channel analog input.                                 |

| 43         | BIN                          |      | BLUE channel analog input.                                  |

|            |                              | 1    | 0.5V~1.0V full scale input. Each input signal is AC-coupled |

|            |                              |      | to each pin and clamp operation is executed.                |

| 30         | HSYNC                        | DI   | Horizontal SYNC input.                                      |

| 50         |                              |      | Reference Clock input to generate DTCLK clock by the        |

|            |                              |      | on-chip PLL (it is also possible to input Sync-On-Green     |

|            |                              |      | signal on SOGIN pin as Reference Clock).                    |

|            |                              | 1    | Active polarity of input signal is selectable by register   |

|            |                              |      | setting.                                                    |

|            |                              | 1    | Leading edge is used for this and trailing edge is ignored. |

| 31         | VSYNC                        | DI   | Vertical SYNC input.                                        |

| 91         | VOINU                        |      |                                                             |

| 10         | GOGDI                        | A.T. |                                                             |

| 49         | SOGIN                        |      | Sync-On-Green input.                                        |

|            |                              |      | Comparator input pin to extract SYNC signal from            |

|            |                              |      | Sync-On-Green signal                                        |

| Comparator input pin to extract SINC signal from       |  |  |  |  |  |

|--------------------------------------------------------|--|--|--|--|--|

| Sync-On-Green signal.                                  |  |  |  |  |  |

| Comparator threshold level is adjustable by register   |  |  |  |  |  |

| setting $(10 \sim 320 \text{mV} / \text{step})$ .      |  |  |  |  |  |

| When this pin is not used, connect to AVDD directly or |  |  |  |  |  |

| connect to AVSS via a 1nF capacitor.                   |  |  |  |  |  |

| ±                                                      |  |  |  |  |  |

| 38               | TEST         | DI         | Test pin.                                                                                                                       |

|------------------|--------------|------------|---------------------------------------------------------------------------------------------------------------------------------|

|                  |              |            | Connect to AVSS. This pin has an on-chip pull-down                                                                              |

|                  |              | DI         | resistor.                                                                                                                       |

| 29               | COAST        | DI         | Clock control coast input.                                                                                                      |

|                  |              |            | Upon application of this Coast input, PLL stops to                                                                              |

|                  |              |            | synchronize with Horizontal SYNC signal and starts to                                                                           |

|                  |              |            | self-run the oscillation.                                                                                                       |

|                  |              |            | It is also possible to use internally generated timing from<br>VSYNC, without using this pin. Connect to AVSS when<br>not used. |

| 24               | CLAMP        | DI         | External Clamp input.                                                                                                           |

| - 1              |              | 21         | Input pin to select timing in order to clamp Video input to                                                                     |

|                  |              |            | an internal, pre-set value.                                                                                                     |

| 26               | TEST2        | DI         | Test pin.                                                                                                                       |

|                  |              |            | Connect to PVDD through MOS SW internally.                                                                                      |

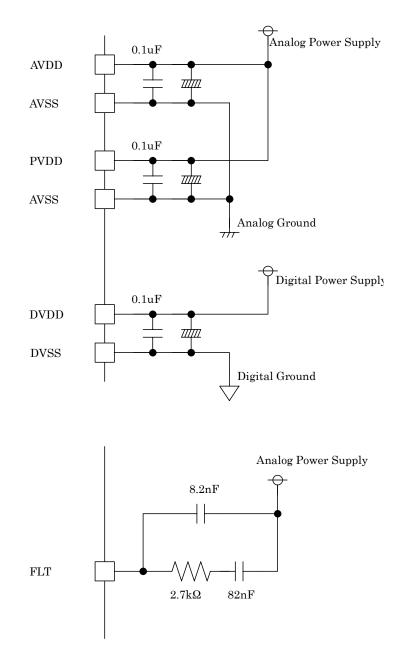

| Decoup           | ling capacit | tor etc. c | connection pins                                                                                                                 |

| 58               | BYPASS       | AO         | Bypass capacitor connection pin for Reference Voltage.                                                                          |

|                  |              |            | Connect a 0.1uF capacitor between this pin and AVSS.                                                                            |

| 37               | BIAS         | AO         | Bias Current pin for internal Analog circuit.                                                                                   |

|                  |              |            | Connect a $6.8k\Omega \pm 1\%$ resistor between this pin and AVSS.                                                              |

| 33               | FLT          | AO         | External Filter connection pin for PLL.                                                                                         |

|                  |              |            | This pin is internally fixed to PVDD at power-down mode.                                                                        |

|                  | Supply pins  |            |                                                                                                                                 |

| 39 42            | AVDD         | PWR        | Analog power supply pins.                                                                                                       |

| 45 46            |              |            |                                                                                                                                 |

| 51 52            |              |            |                                                                                                                                 |

| 59               | DUDD         | DIUD       |                                                                                                                                 |

| 11               | DVDD         | PWR        | Digital power supply pins.                                                                                                      |

| 2367             |              |            |                                                                                                                                 |

| $\frac{78}{27}$  | PVDD         | PWR        | Power supply pins for PLL.                                                                                                      |

| 3435             |              | 1 1/11     | Tower supply plus for TLL.                                                                                                      |

| 25 28            | AVSS         | PWR        | Analog ground pins.                                                                                                             |

| 32 36            |              |            |                                                                                                                                 |

| 40 41            |              |            |                                                                                                                                 |

| $44\ 47$         |              |            |                                                                                                                                 |

| $50\ 53$         |              |            |                                                                                                                                 |

| 60               |              |            |                                                                                                                                 |

| 10,22            | DVSS         | PWR        | Digital ground pins.                                                                                                            |

| 66,79            |              |            |                                                                                                                                 |

| NC Pin           |              | NG         |                                                                                                                                 |

| 8,9,             | NC           | NC         | NC pins. Left open.                                                                                                             |

| $20,21 \\ 76,77$ |              |            |                                                                                                                                 |

|                  | 1            |            |                                                                                                                                 |

AI : Analog Input pin, AO : Analog Output pin

DI : Digital Input pin, DO : Digital Output pin, PWR : Power Supply / Ground pin

DI pins be free from Hi-Z input.

DO pins set to be Hi-Z output state by register setting.

# ■ Absolute Maximum Ratings

| ground level)                                           |        |          |          |      |                                                               |

|---------------------------------------------------------|--------|----------|----------|------|---------------------------------------------------------------|

| Item                                                    | Symbol | Min      | Max      | Unit | Note                                                          |

| Power Supplies                                          |        |          |          |      |                                                               |

| Analog                                                  | AVDD   | -0.3     | 4.5      | V    |                                                               |

| Digital                                                 | DVDD   | -0.3     | 4.5      | V    |                                                               |

| PLL                                                     | PVDD   | -0.3     | 4.5      | V    |                                                               |

| Input Current<br>(excluding power<br>supply pins)       | IIN    |          | ±10      | mA   |                                                               |

| Analog Input<br>Voltage                                 | VINA   | AVSS-0.3 | AVDD+0.3 | V    | RIN, GIN, BIN,<br>SOGIN                                       |

| Digital Input<br>Voltage                                | VINL   | AVSS-0.3 | AVDD+0.3 | V    | SDA, SCL, A0,<br>RESETN                                       |

| Digital Input<br>Voltage                                | VINL2  | AVSS-0.3 | PVDD+0.3 | V    | VSYNC, HSYNC,<br>CLAMP, COAST,<br>TEST, TEST2                 |

| Input Voltage at<br>Hi-Z condition<br>(Data Output pin) | VONL   | DVSS-0.3 | DVDD+0.3 | V    | ROUT,GOUT,BO<br>UT,<br>HSYNCO,<br>VSYNCO,<br>SOGOUT,<br>DTCLK |

| Storage<br>Temperature                                  | Tstg   | -65      | 150      | °C   |                                                               |

Table 3 : Absolute Maximum Ratings (AVSS, DVSS = 0V : all voltages are referenced to ground level)

(note) Operation under a condition exceeding above limits may cause permanent damage to the device. Normal operation is not guaranteed under the above, extreme conditions.

■ Recommended Operating Conditions

At the power-up, the AK5406 device must be reset using RESETN pin. Table 4 : Recommended Operating Conditions

| (AVSS, DVSS = 0V : all voltages are referenced to ground level |        |     |     |     |      |      |  |  |

|----------------------------------------------------------------|--------|-----|-----|-----|------|------|--|--|

| Item                                                           | Symbol | Min | TYP | MAX | Unit | Note |  |  |

| Power Supplies                                                 |        |     |     |     |      |      |  |  |

| Analog                                                         | AVDD   | 3.0 | 3.3 | 3.6 | V    |      |  |  |

| Digital                                                        | DVDD   | 3.0 | 3.3 | 3.6 | V    |      |  |  |

| PLL                                                            | PVDD   | 3.0 | 3.3 | 3.6 | V    |      |  |  |

| Operating<br>Temperature Range                                 | Та     | -40 |     | 85  | °C   |      |  |  |

Electrical Characteristics

1) Analog Characteristics

(AVDD = DVDD = PVDD = 3.3V, Ta = 25°C, sampling frequency at 80 MSPS, input signal frequency = 1MHz, input signal amplitude = -2 dBFS unless otherwise noted ) Table 5.

| Item                       | Symbol        | Conditions                  | MIN | TYP       | MAX       | Unit   |

|----------------------------|---------------|-----------------------------|-----|-----------|-----------|--------|

| Input Range                |               |                             |     |           |           |        |

| at maximum gain            | IRNG1         |                             |     |           | 0.5       | V      |

| at minimum gain            | IRNG2         |                             | 1.0 |           |           | V      |

| Input Full Scale           | IRNGM         | at minimum gain             |     |           | 10        | %FS    |

| Matching                   | minum         | at infinition gain          |     |           | 10        | 701 0  |

| Static Characteristics     |               |                             |     |           |           |        |

| Differential Non-Linearity | DNL           | (note 1)                    |     | $\pm 0.5$ | $\pm 1.0$ | LSB    |

| Integral Non-Linearity     | INL           | (note 1)                    |     | $\pm 1.0$ | $\pm 3.0$ | LSB    |

| Offset                     | VOF           |                             |     |           | $\pm 47$  | LSB    |

| Dynamic Characteristics    |               |                             |     |           |           |        |

| S/N                        | SNR           |                             |     | 46        |           | dB     |

| Cross-Talk                 | $\mathbf{CT}$ | Input Frequency = $7.5 MHz$ |     | 55        |           | dBc    |

| PLL Jitter                 | TJ            | (note 2)                    |     | 300       |           | ps rms |

| Power Dissipation          |               |                             |     |           |           |        |

| Analog                     | IA            |                             |     | 180       |           | mA     |

| Digital                    | ID            | (note 3)                    |     | 24        |           | mA     |

| PLL                        | IP            |                             |     | 15        |           | mA     |

| Total                      | IT            |                             |     | 219       | 290       | mA     |

| At Power-Down              | IPD           | (note 4)                    |     | 1.5       | 2.6       | mA     |

(note 1) Measured at gain = 80H (Address : 08H, 09H, 0AH)

(note 2) VCO range = 2H, charged pump current = 3H (Address : 05H), PLL Div : 2200(897H), fH=33.75kHz, CLK=74.25MHz

(note 3) Capacitive loadings

CL = 15 pF (DTCLK pin)

CL = 5pF (ROUT, GOUT, BOUT, HSYNCO, VSYNCO pins)

(note 4) During power-down, SOG Slicer & Slicer VREF and I<sup>2</sup>C Control circuits are active.

# 2) Digital Input / Output DC Characteristics

| $(AVDD = DVDD = PVDD = 3.0 \sim 3.6V, AVSS = DVSS = 0v, Ta = -40 \sim 85^{\circ}$ |            |                                                                                   |          |         |         |      |  |  |

|-----------------------------------------------------------------------------------|------------|-----------------------------------------------------------------------------------|----------|---------|---------|------|--|--|

| Item                                                                              | Symbo<br>l | Condition                                                                         | MIN      | TY<br>P | MAX     | Unit |  |  |

| High Level Input<br>Voltage                                                       | VIH        | A0, RESETN pins                                                                   | 0.7AVDD  |         |         | V    |  |  |

| Low Level Input<br>Voltage                                                        | VIL        | A0, RESETN pins                                                                   |          |         | 0.3AVDD | V    |  |  |

| High Level Input<br>Voltage                                                       | VIHP       | VSYNC, HSYNC,<br>COAST, CLAMP<br>pins                                             | 0.7PVDD  |         |         | v    |  |  |

| Low Level Input<br>Voltage                                                        | VILP       | VSYNC, HSYNC,<br>COAST, CLAMP<br>pins                                             |          |         | 0.3PVDD | V    |  |  |

| Input Pin<br>Leakage Current                                                      | ILIKG      | HSYNC,VSYNC,CL<br>AMP, COAST pins                                                 |          |         | ±10     | uA   |  |  |

| High Level<br>Output Voltage                                                      | VOH        | ROUT, GOUT,<br>BOUT, HSYNCO,<br>VSYNCO,<br>SOGOUT pins<br>IOH=-1mA                | DVDD-0.5 |         |         | V    |  |  |

| Low Level Output<br>Voltage                                                       | VOL        | ROUT, GOUT,<br>BOUT, HSYNCO,<br>VSYNCO,<br>SOGOUT pins<br>IOL=1mA                 |          |         | 0.5     | V    |  |  |

| DTCLK pin<br>High Level<br>Output Voltage                                         | VOHC       | DTCLK pin<br>IOH= -4mA                                                            | DVDD-0.5 |         |         | V    |  |  |

| DTCLK pin<br>Low Level Output<br>Voltage                                          | VOLC       | DTCLK pin<br>IOL= 4mA                                                             |          |         | 0.5     | v    |  |  |

| Hi-Z Leakage<br>Current                                                           | IOZ        | ROUT, GOUT,<br>BOUT<br>HSYNCO,<br>VSYNCO,<br>SOGOUT, DTCLK<br>pins at Hi-Z output |          |         | ±10     | uA   |  |  |

| I <sup>2</sup> C<br>High Level Input<br>Voltage                                   | VIH2       | SDA, SCL pins                                                                     | 0.7AVDD  |         |         | v    |  |  |

| I <sup>2</sup> C<br>Low Level Input<br>Voltage                                    | VIL2       | SDA, SCL pins                                                                     |          |         | 0.3AVDD | V    |  |  |

| I <sup>2</sup> C<br>Low Level Output<br>Voltage                                   | VOL2       | SDA pin,<br>IOL=3mA                                                               |          |         | 0.4     | V    |  |  |

Table 6 : Digital DC Characteristics (AVDD = DVDD = PVDD =  $3.0 \sim 3.6V$ , AVSS = DVSS= 0v, Ta =  $-40 \sim 85^{\circ}C$ )

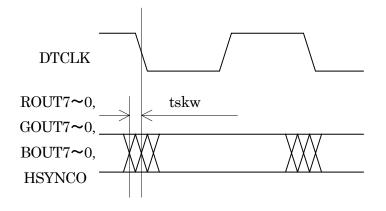

3) Switching Characteristics

Table 7 : Switching Characteristics

```

(AVDD = DVDD = PVDD = 3.0 ~ 3.6V, AVSS = DVSS = 0V, Ta = -40 ~ 85°C, CL of DTCLK pin = 15pF, CL of ROUT, GOUT, BOUT, HSYNCO pins = 5pF)

```

| Item                     | Symbol | Condition                                                        | MIN  | TYP | MAX | Unit |

|--------------------------|--------|------------------------------------------------------------------|------|-----|-----|------|

| Conversion Speed         |        |                                                                  |      |     |     |      |

| maximum                  | fsmax  |                                                                  | 80   |     |     | MSPS |

| minimum                  | fsmin  |                                                                  |      |     | 9   | MSPS |

| DTCLK duty               |        |                                                                  | 42   | 50  | 58  | %    |

| Data Skew                | tskw   | Referenced to the<br>Falling edge of<br>DTCLK output<br>(note 1) | -1.0 |     | 4.0 | ns   |

| HSYNC Input<br>Frequency |        |                                                                  | 15   |     | 110 | kHz  |

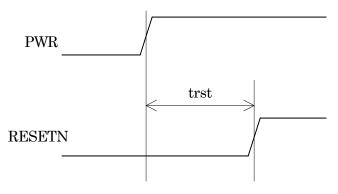

| Reset Timing             | trst   | After the power-up                                               | 1    |     |     | us   |

(note 1) 1/2 of VDD referenced

Fig. 5 Reset Timing

# 4) Serial I/F Switching Characteristics

| Table 8 | 3: Serial | I/F | Switching | Characteristics |

|---------|-----------|-----|-----------|-----------------|

|         |           |     |           |                 |

| (AVDI             | $(AVDD = DVDD = PVDD = 3.0 \sim 3.6V, AVSS = DVSS = 0V, Ta = -40 \sim 85^{\circ}C)$ |           |     |     |     |      |  |  |  |

|-------------------|-------------------------------------------------------------------------------------|-----------|-----|-----|-----|------|--|--|--|

| Item              | Symbol                                                                              | Condition | MIN | TYP | MAX | Unit |  |  |  |

| Bus Free Time     | $t_{ m BUF}$                                                                        |           | 1.3 |     |     | us   |  |  |  |

| Hold Time         | <b>+</b>                                                                            |           | 0.0 |     |     |      |  |  |  |

| (Start Condition) | thd:sta                                                                             |           | 0.6 |     |     | us   |  |  |  |

| Clock Pulse       | 4                                                                                   |           | 1.0 |     |     |      |  |  |  |

| Low Time          | tlow                                                                                |           | 1.3 |     |     | us   |  |  |  |

| Input Signal      | 4                                                                                   |           |     |     | 200 |      |  |  |  |

| Rise Time         | $t_{ m R}$                                                                          |           |     |     | 300 | ns   |  |  |  |

| Input Signal      | 4                                                                                   |           |     |     | 200 |      |  |  |  |

| Fall Time         | $t_{ m F}$                                                                          |           |     |     | 300 | ns   |  |  |  |

| Setup Time        | tarram.                                                                             |           | 0.0 |     |     |      |  |  |  |

| (Start Condition) | tsu:sta                                                                             |           | 0.6 |     |     | us   |  |  |  |

| Setup Time        | tarramo                                                                             |           | 0.6 |     |     | 110  |  |  |  |

| (Stop Condition)  | t <sub>SU:STO</sub>                                                                 |           | 0.0 |     |     | us   |  |  |  |

The above  $I^2 C$  bus related timings are  $I^2 C$  Bus Specifications, and they are not the device limits.

For details, refer to  $I^{2}C$  Bus Specifications.

Fig. 6 Serial Control Timing

## ASAHI KASEI

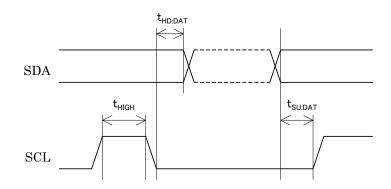

| Table 9. $(AVDD = DVDD = PVDD = 3.0 \sim 3.6V, AVSS = DVSS = 0V, Ta = -40 \sim 85^{\circ}C$ |         |           |                 |     |                 |      |  |

|---------------------------------------------------------------------------------------------|---------|-----------|-----------------|-----|-----------------|------|--|

| Item                                                                                        | Symbol  | Condition | MIN             | TYP | MAX             | Unit |  |

| Data Setup Time                                                                             | tsu:dat |           | 100<br>(note 1) |     |                 | ns   |  |

| Data Hold Time                                                                              | thd:dat |           | 0.0             |     | 0.9<br>(note 2) | us   |  |

| Clock Pulse<br>High Time                                                                    | thigh   |           | 0.6             |     |                 | us   |  |

Table 0 0 0 10  $\alpha = \alpha \alpha$ סמעת 0.017 17700 DVaa

(note 1) when to use in I<sup>2</sup>C Bus Standard mode, t<sub>SU:DAT</sub>≥250ns must be satisfied. (note 2) when the AK5406 is used on non-extended the bus (used at the =minimum specification), this condition must be satisfied.

Fig. 7 Serial Control Timing (#2)

Functional Description

ADC

10-bit 80 MSPS A/D Converter, output is reduced to 8-bit.

## **Reset Operation**

Reset Operation must be executed after the power-up.

Reset pulse can be fed in asynchronous fashion, with a pulse width of longer than 1 us. Right after the reset operation, registers are set to their default.

## PLL Function

The Pixel Clock is re-produced by PLL based on HSYNC to be input.

The AK5406 is corresponds from 9MHz to 80MHz of frequency by adjusting Charged Pump Current as PLL parameter.

The example of Charged Pump current calculation is shown below, and the closest value is setting to register (Address 0x03 bit 5:3).

AK5406 PLL Cpcurrent (CPI) calculation :

CPI = ((2pi\*fH)/NFRatio)^2\*C\*N\*P / Kvco;

fH : PLL reference signal (Horizontal SYNC signalin [Hz] )

NFRatio : Set to each natural frequency Reference signal is divided and set to 13.

C: 0.082uF

N: PLL divide ratio (Register Address 0x01, 0x02)

P: 4:<9-32MHz>, 2:<32-64MHz>, 1:<64-80MHz> Clock Frequency range.

Kvco: 130MHz

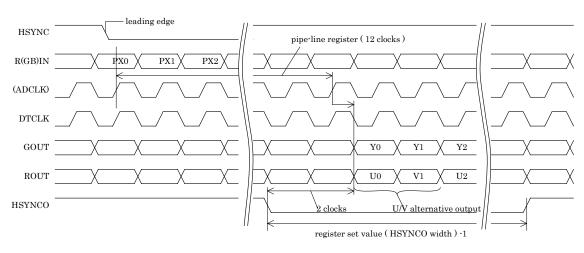

## PLL Coast Funtion

The Pixel Clock is re-produced by PLL based on HSYNC to be input. Coast mode is to cease its PLL tracking operation and to let VCO self-run.

There are 2 modes in Coast function –

One is HSYNC Pulse Duration Coast where the duration time is selected from Pre-VSYNC timing as start point and Post-VSYNC timing as stop point, and the other is to input directly on Coast pin a signal to notify its timing.

(refer to timing diagram 3) Coast Timing)

## **Clamp Function**

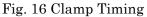

This is a function to adjust reference level of AC-coupled input signal to match with the AK5406 internal reference level. It is required to specify a specific period where reference level of input signal is being input. It is selectable to specify the period by external CLAMP pin or by register setting. If the clamp period is specified by register, the position and the period from the trailing edge of HSYNC are set to the register. (refer to timing diagram 4) Clamp Timing #1)

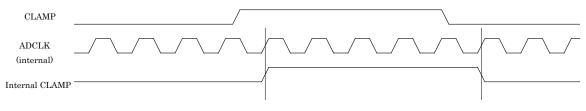

During the clamp period the Analog Clamp circuit (Clamp Block) and the Black Loop circuit (Black Loop block) are operational at the same timing at the default setting. It is possible to set the Analog Clamp at the first half of clamp period and Black Loop at the other half during the clamp period by register setting. ((refer to timing diagram 5) Clamp timing #2) Clamp function can be coasted as in the case of PLL ((refer to timing diagram 6) Clamp Coast).

It is also possible by register setting to clamp the minimum value in accordance with RGB signals or to clamp the center value in accordance with YUV signals (refer to register address 10H).

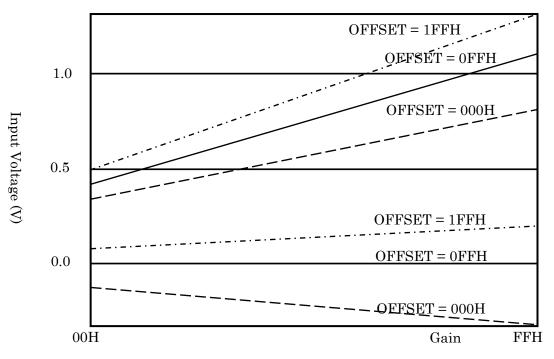

## **Gain Adjust Function**

ADC Full-Scale Input Range is adjustable within  $0.5V \sim 1V$  by PGA (Programmable Gain Amplifier). PGA has an 8-bit resolution.

# SYNC Separation Function

MS0592-E-01

VSYNC is extracted from the internal Slicer output.

## Black Loop Function, Offset Adjust Function

With a help of Black Loop operation during the Clamp period, offset of internal circuit can be eliminated and Clamp level is retained to the set value.

Black level is arbitrarily pre-settable for each of 3 channels independently, in the range from -4 to +20 by Black Loop Setting Value setting register.

In addition to enabling Black Loop function always during the Clamp period, it is also possible to control Black Loop function to operate or to hold the condition by register setting.

Black Loop function can be completely disabled.

Only in this case, each of channel offset adjust registers is valid and external offset adjustment is enabled.

Gain Offset Control diagram below shows its relation.

Fig. 8 Gain Offset Control

## Control Serial I/F

This is a control register with I<sup>2</sup>C Serial Interface.

An external pull-up resistor should be connected on SDA pin.

Data on SDA line is captured at the rising edge of SCL.

Make certain that Data on SDA line changes state only during SCL at low condition.

When SDA changes state while SCL is at high condition, it is interpreted to be a Start condition if the change occurs at the falling transition, and it is to be a Stop condition if it occurs at the rising transition.

## ASAHI KASEI

## [I<sup>2</sup>C Slave Address]

I<sup>2</sup>C Slave Address is selectable to be either 1001100 or 1001101 by AO pin setting.

| A0 pin | I <sup>2</sup> C Slave Address |

|--------|--------------------------------|

| LO     | 1001100                        |

| HI     | 1001101                        |

[I<sup>2</sup>C Write Sequence]

When the Slave Address of the AK5406 Write Mode is received at the First Byte, Sub-Address at the Second Byte and Data at the Third & Succeeding Bytes are received.

There are 2 operations in Write sequence –

(a) Single Byte Write Sequence

| s | Slave<br>Address | w             | Α  | Sub<br>Address |    | Data                                            | A  | Stp |

|---|------------------|---------------|----|----------------|----|-------------------------------------------------|----|-----|

|   | < 8b             | $\rightarrow$ | 1b | <>             | 1b | $\langle \overset{8b}{\longrightarrow} \rangle$ | 1b |     |

Fig. 9a Single Byte Write Sequence

(b) Multiple Byte (m bytes) Write Sequence (Sequential Write operation)

| s | Slave<br>Address | w             | Α  | Sub<br>Address(n) | Α  | Data(n)                              | A  | Data(n+1)                                       | Α  | <br>Data(n+m)                        | Α  | Stp |

|---|------------------|---------------|----|-------------------|----|--------------------------------------|----|-------------------------------------------------|----|--------------------------------------|----|-----|

|   | < 8b             | $\rightarrow$ | 1b | < 8b              | 1b | $\stackrel{8b}{\longleftrightarrow}$ | 1b | $\langle \overset{8b}{\longrightarrow} \rangle$ | 1b | $\stackrel{8b}{\longleftrightarrow}$ | 1b |     |

Fig. 9b Sequential Write

(c) Read Sequence

When the Slave Address of the AK5406 Read Mode is received at the First Byte, Data at the second & Succeeding Bytes transmitted from the AK5406.

| s | Slave<br>Address | w             | Α  | Sub<br>Address(n) | Α  | rS | Slave<br>Address | R             | Α  | Data1                                           | Α  | Data2                                           | Α  | <br>Data n  | Ā  | Stp |

|---|------------------|---------------|----|-------------------|----|----|------------------|---------------|----|-------------------------------------------------|----|-------------------------------------------------|----|-------------|----|-----|

|   | < 8b             | $\rightarrow$ | 1b | < <u></u> >       | 1b | ¥  | < 8b             | $\rightarrow$ | 1b | $\langle \overset{8b}{\longrightarrow} \rangle$ | 1b | $\langle \overset{8b}{\longrightarrow} \rangle$ | 1b | < <u>8b</u> | 1b |     |

Fig. 9c Read Sequence

Abbreviation terms listed above mean :

- S,rS Start Condition

- 0:Acknowledge (SDA Low) А (SDA High)

- Ā 1:Not Acknowledge

Stp **Stop Condition**

- R/W 1:Read, 0:Write

- To be controlled by the Master device. To be output by micro-computer normally.

- To be controlled by the Slave device. To be output by the AK5406.

# ■ Timing Charts

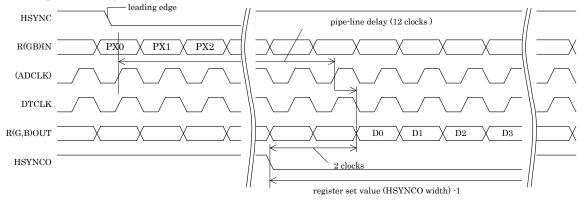

## 1) Output Timing

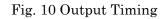

2) 4 : 2 : 2 Output Mode Timing

### Reference register address 07H : (HSYNCO WIDTH) 0EH : HSYNC POL, HSYNCO POL

Fig. 114:2:2Output Mode Timing

Reference register address 15H : Output Format

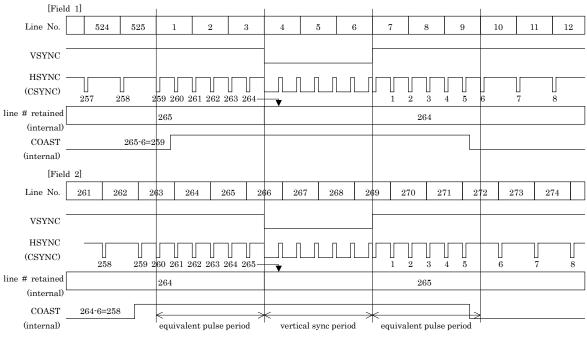

(note) Since PRE-COAST time is counted, based on # of lines in the previous Field, there is a case in the interlaced signal mode that COAST period may slightly differ between Odd Field case and Even Field case.

\*525i Mode COAST example

(in case of register pre-coast = 6, register post-coast = 5)

Fig. 14 COAST Timing (525i Mode Coast example)

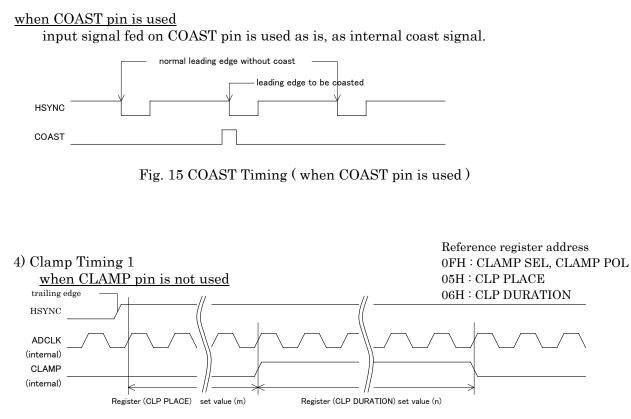

when CLAMP pin is used Externally feds clamp timing pulse from CLAMP pin. Clamp timing pulse be sampled by ADCLK then used internally.

Fig. 17 Clamp Timing

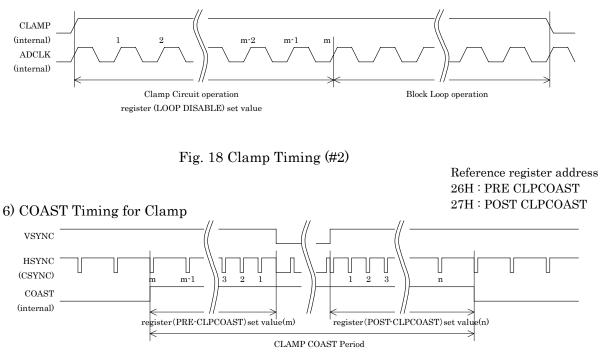

# 5) CLAMP Timing 2

When register (LOOP DISABLE) is set to value (m) other than 0, the clamp period is divided into 2 half where it is possible that the Clamp Circuit operational at First half of the period (m pixels clock) and Black Loop at the other half.

When m = 0 (reset value), the Clamp Circuit and the Black Loop are operate at the same timing.

Fig. 19 Clamp Coast Timing

(note) Since PRE CLPCOAST time is counted, based on # of lines in the previous Field, there is a case in the interlaced signal mode that COAST period may slightly differ between Odd Field and Even Field case.

For details, refer to (3) COAST Timing section.

# ■ Control Register

Table 11 : Register map

|                |               | ner ma      |                               | 1                 |                                          |

|----------------|---------------|-------------|-------------------------------|-------------------|------------------------------------------|

| Sub            | R/W           |             | Default                       | Register          |                                          |

| Adrs           | Or            | Bits        | Value                         | Name              | Function                                 |

|                | RO            |             |                               |                   |                                          |

| 00H            | RO            | 7:0         | 10101110                      | CHIPID            | Device ID number                         |

| 01H            | R/W           | 7:0         | 01101001                      | PLL DIV           | Upper 8-bit PLL divider ratio[11:4]      |

| 0111           |               |             | 01101001                      | (MSB)             |                                          |

|                |               |             |                               |                   |                                          |

| 02H            | R/W           | 7:4         | 1101****                      | PLL DIV           | Lower 4-bit PLL divider ratio[3:0]       |

|                |               |             |                               | (LSB)             |                                          |

| 03H            | R/W           | 7:6         | 01*****                       | PLL VCO           | Bit [7:6] PLL VCO range                  |

|                |               | 5:3         | **001***                      | PLL CP            | Bit [5:3] PLL Charged Pump current       |

| 04H            | R/W           | 7:3         | 10000***                      | PHADJ             | Clock phase adjust (1LSB = T/32)         |

| 05H            | R/W           | 7:0         | 10000000                      | CLP PLACE         | Clamp position                           |

| 06H            | R/W           | 7:0         | 10000000                      | CLP               | Clamp period                             |

| 0011           | 10/ 10        | 7.0         | 10000000                      | DURATION          | Clamp period                             |

| 07H            | R/W           | 7:0         | 00100000                      | HSYNCO            | HSYNCO pulse width                       |

| 07П            | <b>ГС/ VV</b> | 7.0         | 00100000                      |                   | ns i NCO pulse width                     |

| 0.011          | DAV           | <b>7</b> :0 | 10000000                      | WIDTH<br>DED CAIN |                                          |

| 08H            | R/W           | 7:0         | 1000000                       | RED GAIN          | Red channel gain adjust                  |

| 09H            | R/W           | 7:0         | 10000000                      | GREEN             | Green channel gain adjust                |

|                |               |             |                               | GAIN              |                                          |

| 0AH            | R/W           | 7:0         | 10000000                      | BLUE GAIN         | Blue channel gain adjust                 |

| 0B-0DH         | RO            | 7:0         | 00000000                      |                   | Reserved                                 |

| 0EH            |               |             | *1*****                       | HSYNC POL         |                                          |

| UEH            | R/W           | 6           | .1                            | HSINCPOL          | Bit 6 : HSYNC input polarity setting     |

|                |               | -           | **0****                       | HONDIGO           | (0:Low 1:Hi)                             |

|                |               | 5           | **0****                       | HSYNCO            | Bit 5 : HSYNCO output polarity setting   |

|                |               | 9           | ****0***                      | POL               | (0:Hi  1:Low)                            |

|                |               | 3           | ****0***                      | HSYNC SEL         | Bit 3 : Hsync select                     |

|                |               | 0           | ماد ماد 🔿 ماد ماد ماد ماد ماد |                   | (0:HSYNC 1: Sync-on-Green)               |

|                |               | 2           | *****0**                      | VSYNC POL         | Bit 2 : VSYNCO inversion                 |

|                |               | 0           | ******0                       |                   | $(0: INV  1: N_0 INV)$                   |

|                |               | 0           | ******0                       | VSYNC SEL         | Bit 0 : VSYNC select                     |

|                |               |             |                               |                   | (0 at power-down(PDN=0))                 |

|                |               | _           |                               |                   | (0:VSYNC 1:Sync Separator Signal)        |

| $0\mathrm{FH}$ | R/W           | 7           | 0******                       | CLAMP SEL         | Bit 7: Clamp signal select               |

|                |               |             | at an atom to the the         |                   | (0:HSYNC 1:CLAMP pin)                    |

|                |               | 6           | *1*****                       |                   | Bit 6: Clamp polarity (0: Hi 1: Low)     |

|                |               | 5           | **0****                       | COAST SEL         | Bit 5: Coast select                      |

|                |               |             |                               | 00100000          | (0: COAST Pin 1: VSYNC)                  |

|                |               | 3           | ****1***                      | COAST POL         | Bit 3: Coast polarity setting            |

|                |               |             |                               |                   | (0:Low 1:Hi)                             |

|                |               | 1           | *****1*                       | PDN               | Bit 1: Power-down                        |

|                |               |             |                               |                   | (0:power-down 1:normal operation)        |

| 10H            | R/W           | 7:3         | 10111***                      | SOGTH             | Sync-on- Green threshold level setting   |

|                |               | 2           | *****0**                      | RED CLP           | Bit 2: Red channel clamp level setting   |

|                |               |             |                               | LVL               | (0:Minimum value 1:Mid value)            |

|                |               | 1           | *****0*                       | GREEN CLP         | Bit 1: Green channel clamp level setting |

|                |               |             |                               | LVL               | (0:Minimum value 1:Mid value)            |

|                |               | 0           | ******0                       | BLUE CLP          | Bit 0: Blue channel clamp level setting  |

|                |               |             |                               | LVL               | (0:Minimum value 1:Mid value)            |

| L              | l             | 1           |                               |                   |                                          |

| Sub  | R/W   |      | Default  | Register    |                                        |

|------|-------|------|----------|-------------|----------------------------------------|

| Adrs | Or RO | Bits | Value    | Name        | Function                               |

| 11H  | R/W   | 7:0  | 00100000 | SSEPTH      | Sync Separator threshold level setting |

| 12H  | R/W   | 7:0  | 00000000 | PRE COAST   | Pre-Coast                              |

| 13H  | R/W   | 7:0  | 00000000 | POST COAST  | Post-Coast                             |

| 14H  | RO    | 7:0  | 00000000 | RESERVE     | Reserved                               |

| 15H  | R/W   | 1    | *****1*  | OUTPUT      | Bit1 : Output Format                   |

|      |       |      |          | FORMAT      | (0: 4:2:2, 1:4:4:4)                    |

| 16H  | R/W   | 7:0  | ******   |             | Don't care                             |

| 17H  | R/W   | 0    | ******1  | RED OFFSET  | Red channel offset adjust (MSB)        |

|      |       |      |          | (MSB)       |                                        |

| 18H  | R/W   | 7:0  | 00000000 | RED OFFSET  | Red channel offset adjust (LSB)        |

|      |       |      |          | (LSB)       |                                        |

| 19H  | R/W   | 0    | ******1  | GREEN       | Green channel offset adjust (MSB)      |

|      |       |      |          | OFFSET      |                                        |

|      |       |      |          | (MSB)       |                                        |

| 1AH  | R/W   | 7:0  | 00000000 | GREEN       | Green channel offset adjust (LSB)      |

|      |       |      |          | OFFSET      |                                        |

|      |       |      |          | (LSB)       |                                        |

| 1BH  | R/W   | 0    | ******1  | BLUE OFFSET | Blue channel offset adjust (MSB)       |

|      |       |      |          | (MSB)       |                                        |

| 1CH  | R/W   | 7:0  | 00000000 | BLUE OFFSET | Blue channel offset adjust (LSB)       |

|      |       |      |          | (LSB)       |                                        |

Table 12 : Black Loop Registers

| -              |         | трор     | negisters                 | D            | 1                                         |

|----------------|---------|----------|---------------------------|--------------|-------------------------------------------|

| Sub            | R/W     |          | Default                   | Register     |                                           |

| Adrs           | Or      | Bits     | Value                     | Name         | Function                                  |

|                | RO      |          |                           |              |                                           |

| 1DH            | R/W     | 0        | ******0                   | RED BLK LVL  | RED channel black loop setting value      |

|                |         |          |                           | (MSB)        | (MSB)                                     |

| 1EH            | R/W     | 7:0      | 00000000                  | RED BLK LVL  | RED channel black loop setting value      |

| 1111           | 10 11   |          | 00000000                  | (LSB)        | (LSB)                                     |

| 1 1711         | DAV     | 0        | ******0                   |              |                                           |

| $1\mathrm{FH}$ | R/W     | 0        | ******0                   | GREEN BLK    | GREEN channel black loop setting value    |

|                |         |          |                           | LVL          | (MSB)                                     |

|                |         |          |                           | (MSB)        |                                           |

| 20H            | R/W     | 7:0      | 00000000                  | GREEN BLK    | GREEN channel black loop setting value    |

|                |         |          |                           | LVL          | (LSB)                                     |

|                |         |          |                           | (LSB)        |                                           |

| 21H            | R/W     | 0        | ******0                   | BLUE BLK LVL | BLUE channel black loop setting value     |

|                | 10/11   | 0        | Ű                         | (MSB)        | (MSB)                                     |

| 22H            | R/W     | 7:0      | 00000000                  | BLUE BLK LVL | BLUE channel black loop setting value     |

| 2211           | 10/ 00  | 7.0      | 0000000                   |              |                                           |

|                | DATA    |          |                           | (LSB)        | (LSB)                                     |

| 23H            | R/W     | 7:5      | 000*****                  | LBW          | Black Loop bandwidth                      |

|                |         | 4:3      | ***00***                  | LOOPOFFRNG   | Black Loop coring bandwidth control       |

|                |         | 2        | *****0**                  | LOOPMODE     | Black Loop mode                           |

|                |         |          |                           |              | (0 : loop enable 1 : loop disable)        |

|                |         | 1        | *****0*                   | LOOPHOLD     | retention of black loop condition         |

|                |         | 0        | *******0                  | VSYNC        | (0 : active 1 : condition retained)       |

|                |         | 0        | Ŭ                         | UPDATE       | limit black level update frequency to     |

|                |         |          |                           | UIDAIL       |                                           |

| 0.411          | D // IV | 0        | *0*****                   |              | every 64 VSYNC                            |

| 24H            | R/W     | 6        | *0*****                   | COASTGEN SEL | COASTGEN input setting                    |

|                |         |          |                           |              | (0: VSYNC 1: SYNC SEP)                    |

|                |         | <b>5</b> | **0****                   | CLPBW        | Clamp bandwidth setting                   |

|                |         | 4:3      | ***11***                  | Fixed Bit    | Used in fixed condition. Write "11" when  |

|                |         |          |                           |              | to write.                                 |

|                |         | 2        | ****0**                   | SOGOUT POL   | SOGOUT polarity                           |

|                |         |          | -                         |              | $(0: normal \ 1: inverted)$               |

|                |         | 1        | ******0*                  | SOGOUT SEL   | SOGOUT signal select                      |

|                |         | T        | 0                         |              | (0: SOG - 1: HSYNC)                       |

|                |         | 0        | *******0                  | DOEIN        |                                           |

|                |         | 0        |                           | DOFIX        | Output level at power-down mode           |

|                |         |          |                           |              | (0: fixed low 1: fixed high)              |

| 25H            | R/W     | 7:0      | 00000000                  | LOOP DISABLE | Black loop off period during Clamp period |

| 26H            | R/W     | 7:0      | 00000000                  | PRE CLPCOAST | Pre-Coast for clamp signal                |

| 27H            | R/W     | 7:0      | 00000000                  | POST         | Post-Coast for clamp signal               |

|                |         | . 0      |                           | CLPCOAST     | couse for crump orginal                   |

| ្លា            | R/W     | 7:6      | 11*****                   | DATA DRIVE   | ROUT,GOUT,BOUT,HSYNCO,VSYNCO,             |

| 28H            | IV) AA  | 1.0      | 11                        | DATA DRIVE   |                                           |

|                |         |          | staats of or staats staat |              | SOGOUT pin drivability                    |

|                |         | 5:4      | **11****                  | CLOCK DRIVE  | DTCLK pin drivability                     |

| 29H            | R/W     | 7:6      | 10*****                   | Reserved     | reserved                                  |

|                |         | 5:3      | **101***                  | IN RANGE     | accelerate range control of black loop    |

|                |         | 2:1      | *****00*                  | Reserved     | setting                                   |

|                |         | 0        | ******0                   | Reserved     | Reserved                                  |

|                |         | 5        |                           |              | reserved Do not write value other         |

|                |         |          |                           |              | than "0"                                  |

| 0 A TT         | D/117   | 0:0      | *0111001                  |              |                                           |

| 2AH            | R/W     | 6:0      | *0111001                  | Reserved     | Reserved                                  |

| 2BH            | R/W     | 3:0      | *****00                   |              | Reserved                                  |

| $2\mathrm{CH}$ | RO      | 7:0      | 00000000                  |              | Reserved                                  |

|                |         |          |                           | I            | 1                                         |

TEST Register AK5406 has test register address  $0x20 \sim 0x30$ , which could be accessed in normal mode. Do not write without default.

| 2DH            | R/W | 7:0 | 00000000 | TEST | Default Value : 0x00 |

|----------------|-----|-----|----------|------|----------------------|

| 2EH            | R/W | 7:0 | 00000000 | TEST | Default Value : 0x00 |

| $2\mathrm{FH}$ | R/W | 7:0 | 00100000 | TEST | Default Value : 0x20 |

| 30H            | R/W | 7:0 | 00000000 | TEST | Default Value : 0x00 |

Default value of AK5406

| Adr            | R/W | default |

|----------------|-----|---------|

| 00H            | RO  | AEH     |

| 01H            | R/W | 69H     |

| 02H            | R/W | D0H     |

| 03H            | R/W | 48H     |

| 04H            | R/W | 80H     |

| 05H            | R/W | 80H     |

| 06H            | R/W | 80H     |

| 07H            | R/W | 20H     |

| 08H            | R/W | 80H     |

| 09H            | R/W | 80H     |

| 0AH            | R/W | 80H     |

| 0BH            | RO  | 00H     |

| 0CH            | RO  | 00H     |

| 0DH            | RO  | 00H     |

| 0EH            | R/W | 40H     |

| $0\mathrm{FH}$ | R/W | 4AH     |

| 10H            | R/W | B8H     |

| 11H            | R/W | 20H     |

| 12H            | R/W | 00H     |

| 13H            | R/W | 00H     |

| 14H            | RO  | 00H     |

| 15H            | R/W | 02H     |

| 16H            | R/W | 00H     |

| 17H            | R/W | 01H     |

| 18H            | R/W | 00H     |

| 19H            | R/W | 01H     |

| 1AH            | R/W | 00H     |

| 1BH            | R/W | 01H     |

| 1CH            | R/W | 00H     |

| 1DH            | R/W | 00H     |

| 1EH            | R/W | 00H     |

| 1FH            | R/W | 00H     |

| Adr            | R/W | default |

|----------------|-----|---------|

| 20H            | R/W | 00H     |

| $21\mathrm{H}$ | R/W | 00H     |

| 22H            | R/W | 00H     |

| 23H            | R/W | 00H     |

| 24H            | R/W | 18H     |

| $25\mathrm{H}$ | R/W | 00H     |

| 26H            | R/W | 00H     |

| 27H            | R/W | 00H     |

| 28H            | R/W | F0H     |

| 29H            | R/W | A8H     |

| 2AH            | R/W | 39H     |

| 2BH            | R/W | 00H     |

| 2CH            | RO  | 00H     |

Default value is meshed

Description of Register Contents

# Sub Address 00H CHIP ID

When it is read, device ID number (ADH) is returned.

| u | Address 01     | LH ~ 02H FI |                 | · 09DH               |

|---|----------------|-------------|-----------------|----------------------|

|   | 01H            | 02H         | Decimal         | PLL multiplier ratio |

|   | [7:0]          | [7:4]       | notation of 01H |                      |

|   |                |             | [7:0]&02H [7:4] |                      |

|   | 00H            | 0H          | 0               |                      |

|   | 00H            | 1H          | 1               | Inhibited            |

|   | :              | :           | :               | Innoned              |

|   | $0\mathrm{DH}$ | DH          | 221             |                      |

|   | $0\mathrm{DH}$ | EH          | 222             | 223                  |

|   | $0\mathrm{DH}$ | FH          | 223             | 224                  |

|   | 0EH            | 0H          | 224             | 225                  |

|   | :              | :           | :               | :                    |

|   | $\mathbf{FFH}$ | FH          | 4095            | 4096                 |

# Sub Address 01H ~ 02H PLL DIV Default : 69DH

"set-value plus one" becomes multiplier ratio of PLL.

Write operation of MSB side bits ( sub address 01H ) does not initiate PLL operation, and after LSB side data ( sub address 02H ) is written, a multiplier ratio becomes valid and PLL operation is executed.

# Sub Address 03H

## [7:6] PLL VCO

| [7:6] | PLL VCO operating range |

|-------|-------------------------|

| 00    | 9~32MHz                 |

| 01    | 32~64MHz                |

| 10    | 64~80MHz                |

| 11    | Inhibited               |

# [5:3] PLL CP

| [5:3] | PLL charge pump current |  |

|-------|-------------------------|--|

| 000   | 50uA                    |  |

| 001   | 100uA                   |  |

| 010   | 150uA                   |  |

| 011   | 250uA                   |  |

| 100   | 350uA                   |  |

| 101   | 500uA                   |  |

| 110   | 750uA                   |  |

| 111   | Inhibited               |  |

## Sub Address 04H PHADJ

| [7:3]    | ADC sampling clo | ock phase    |

|----------|------------------|--------------|

| 00H      | -180°            |              |

| 01H      | -168.75°         | advances     |

| •        | :                | <b>↑</b>     |

| 0EH      | -22.5°           |              |

| 0FH      | -11.25°          |              |

| 10H      | standard         | l            |

| 11H      | +11.25°          |              |

| 12H      | +22.5°           |              |

|          |                  |              |

| :        | :                | $\downarrow$ |

| :<br>1EH | :<br>+157.5°     | ↓<br>delayed |

Each single step is equal to 11.25 degrees.

A larger number reflects direction of a bigger delay.

|  | Sub | Address | 05H | CLP | PLACE |

|--|-----|---------|-----|-----|-------|

|--|-----|---------|-----|-----|-------|

# Sub Address 06H CLP DURATION

Clamp timing can be internally generated when CLAMP SEL is set to "0". The periods of clamping is start from trailing edge of HSYNC after the delayed of CLP PLACE pixels and its continue according to the setting of CLP DURATION pixels value. (refer to timing chart 4)

Default: 80H

Default: 80H

Default: 20H

Do not set CLP DURATION to "0" when CLP PLACE is set to "0","1","2" value.

# Sub Address 07H HSYNCO WIDTH

This is to set the pulse width of Horizontal SYNC signal which is re-configured by PLL and is output on HSYNCO pin (refer to timing charts 1 & 2). Do not write this register value to "0".

#### [7:0]Input range Gain [Vpp] 00H 0.377High gain 01H 0.380 02H 0.383 1 : : 7FH 0.75180H 0.75481H 0.757: : Low gain FDH 1.123FEH 1.126 FFH 1.129

#### Sub Address 08H ~ 0AH RED (GREEN, BLUE) GAIN

(note) PGA Gain is shown by 543/(128 + N) where (N = 0 ~ 255(DEC)). PGA Gain is set until ADC input range becomes 1.6Vpp.

#### Sub Address 0EH [6] HSYNC POI

| - 10 | DIHSINC PUL |                                        |

|------|-------------|----------------------------------------|

|      | [6]         | HSYNC input pin polarity               |

|      | 0           | Active low<br>( leading edge to fall ) |

|      | 1           | Active high<br>(leading edge to rise)  |

# [5] HSYNCO POL

| [5] | HSYNCO output pin polarity |

|-----|----------------------------|

| 0   | Active high                |

| 0   | (leading edge to rise)     |

| 1   | Active low                 |

| 1   | ( leading edge to fall )   |

# [3] HSYNC SEL

| [3] | HSYNC signal to be input to | Signal to be input to Sync  |  |

|-----|-----------------------------|-----------------------------|--|

|     | PLL                         | Separator                   |  |

| 0   | HSYNC pin                   | HSYNC pin                   |  |

| 1   | Sync-On-Green SLICER        | Sync-On-Green SLICER output |  |

|     | output                      |                             |  |

# [2] VSYNC POL

| [2] | VSYNCO output pin polarity |

|-----|----------------------------|

| 0   | Inverted VSYNC             |

| 1   | Normal VSYNC               |

# [0] VSYNC SEL

| [0] | VSYNC select          |

|-----|-----------------------|

| 0   | VSYNC                 |

| 1   | Sync Separator signal |

(note) Sync Separator circuit is in power down, when bit 1 of PDN register at Sub Address 0FH is "0".

# Sub Address 0FH

[7] CLAMP SEL

| [7] | Clamp signal to be used at CLP   |

|-----|----------------------------------|

| 0   | Internally generated signal from |

|     | HSYNC                            |

| 1   | CLAMP pin                        |

# [6] CLAMP POL

| [6] | CLAMP input pin polarity |

|-----|--------------------------|

| 0   | Active high              |

| 1   | Active low               |

# [5] COAST SEL

| [5] | [5] Signal to be used as PLL COAST        |  |

|-----|-------------------------------------------|--|

| 0   | COAST pin                                 |  |

| 1   | Internally generated signal from<br>VSYNC |  |

# [3] COAST POL

| [3] | COAST input pin polarity |

|-----|--------------------------|

| 0   | Active low               |

| 1   | Active high              |

# [1] PDN

| [1] | Power-down control | Operating functional blocks  |

|-----|--------------------|------------------------------|

| 0   | Power-down         | VREF<br>Sync-On-Green SLICER |

| 1   | Normal operation   | Total circuit                |

# Sub Address 10H

| [7:3] SOGTH | Default : 17H                           |

|-------------|-----------------------------------------|

| [7:3]       | SOG SLICER threshold level              |

|             | (upward direction from SOG clamp level) |

| 00H         | 320mV                                   |

| 01H         | 310mV                                   |

| :           | :                                       |

| 1EH         | 20mV                                    |

| 1FH         | 10mV                                    |

# [2:0] RED(GREEN,BLUE) CLP LVL

|   | Input clamp level |

|---|-------------------|

| 0 | Minimum level     |

| 1 | Center level      |

# Sub Address 11H SSEPTH

| [7:0] | Sync Separator threshold level |

|-------|--------------------------------|

| FFH   | Wider pulse width              |

| FEH   | $\uparrow$                     |

| :     |                                |

| 20H   | Standard                       |

| :     |                                |

| 01H   | $\downarrow$                   |

| 00H   | Narrower pulse width           |

# Sub Address 12H PRE COAST

# Sub Address 13H POST COAST

Parameters in order to internally generate PLL COAST signal from VSYNC are set. It is valid only when the COAST SEL bit is "1".

In the PRE-COAST register, # of preceding HSYNC periods to be coasted prior to VSYNC signal, is set and in the POST COAST register, # of succeeding HSYNC periods to be coasted after VSYNC signal, is set (refer to timing chart 3).

## Sub Address 15H

## [1] OUTFORMAT

| [4] | Output Format |

|-----|---------------|

| 0   | 4:2:2         |

| 1   | 4:4:4         |

Input & Output signals vs Channel relation is listed in the following table when 4:2:2 output format is selected (refer to timing chart 1 & 2).

| Channel | Input signal | Output signal |

|---------|--------------|---------------|

| Red     | V            | U/V           |

| Green   | Y            | Y             |

| Blue    | U            | Hi-Z          |

## Sub Address 17H ~ 1CH RED(GREEN, BLUE)OFFSET

| OFFSET adjust ( addition / subtraction ) values |

|-------------------------------------------------|

| -64 LSB                                         |

| -63.75 LSB                                      |

| :                                               |

| -0.25 LSB                                       |

| 0 LSB                                           |

| +0.25 LSB                                       |

| :                                               |

| +63.5 LSB                                       |

| +63.75 LSB                                      |

|                                                 |

OFFSET of each channel is adjusted in 9-bit resolution.

Its center value is 0FFH and it is adjusted in 1/4 LSB per single step.

OFFSET adjust is valid only when black loop is disable ( LOOP MODE = 1 ).

Data Write of MSB bits does not affect the operation and Data value becomes valid when Data write of LSB bits is made.

## Sub Address 1DH ~ 22H RED (GREEN, BLUE) BLK LVL

| BLKLVL     | Black Loop se                                   | tting values                                 |

|------------|-------------------------------------------------|----------------------------------------------|

| [0], [7:0] | At minimum clamp level setting<br>(CLP LVL = 0) | At center clamp level setting<br>(CLP LVL=1) |

| 011111111  | Inhibited                                       | Inhibited                                    |

| 011111110  | Inhibited                                       | Inhibited                                    |

| :          | :                                               | :                                            |

| 001010001  | Inhibited                                       | :                                            |

| 001010000  | 20                                              | :                                            |

| 001001111  | 19.75                                           | :                                            |

|            | :                                               | :                                            |

| 000011101  | 7.25                                            | Inhibited                                    |

| 000011100  | 7                                               | 135                                          |

| 000011011  | 6.75                                            | 134.75                                       |

|            | :                                               | •                                            |

| 000000010  | 0.5                                             | 128.5                                        |

| 000000001  | 0.25                                            | 128.25                                       |

| 00000000   | 0                                               | 128 (200H)                                   |

| 111111111  | -0.25                                           | 127.75                                       |

| 111111110  | -5                                              | 127.5                                        |

| :          | :                                               | :                                            |

| 111110001  | -3.75                                           | 124.25                                       |

| 111110000  | -4                                              | 124                                          |

| 111101111  | Inhibited                                       | 123.75                                       |